JTAG最初是用来对芯片进行测试的,基本原理是在器件内部定义一个TAP(Test Access Port?测试访问口)通过专用的JTAG测试工具对进行内部节点进行测试。JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。现在,JTAG接口还常用于实现ISP(In-System Programmable?在线编程),对FLASH等器件进行编程。

JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程实现再装到板上因此而改变,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。JTAG接口可对PSD芯片内部的所有部件进行编程

简单地说,JTAG的工作原理可以归结为:在器件内部定义一个TAP(TestAccessPort,测试访问口),通过专用的JTAG测试工具对内部节点进行测试和调试。

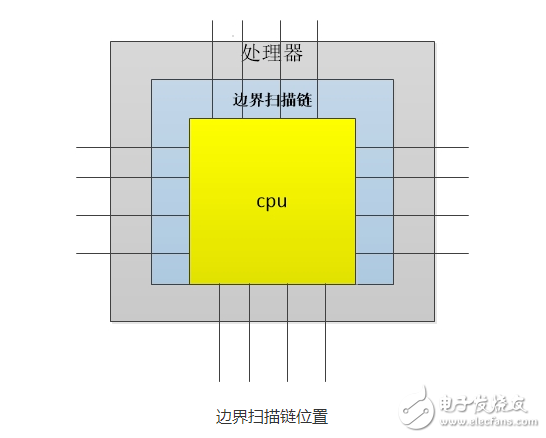

边界扫描边界扫描(Boundary-Scan)即在芯片的每个输入输出管脚上都增加一个移位寄存器单元(Boundary-Scan Register Cell),因为这些移位寄存器单元分布在芯片的边界上,所以被称为边界扫描寄存器。在JTAG 调试中,边界扫描是一个很重要的概念,当需要调试芯片时,这些寄存器将芯片与外围电路隔离,实现对芯片输入输出信号的观察和控制:对于输入管脚,可以通过与之相连的边界扫描寄存器单元把数据加载到该管脚中;对于输出管脚,可以通过与之相连的边界扫描寄存器“捕获”(CAPTURE)该管脚上的输出信号;正常运行状态下,这些边界扫描寄存器单元对芯片是透明的,所以正常的运行不会受到影响。另外,芯片输入输出管脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain),它可以串行的输入和输出,通过相应的时钟信号和控制信号,实现对处在调试状态下的芯片的输入和输出状态的观察和控制。

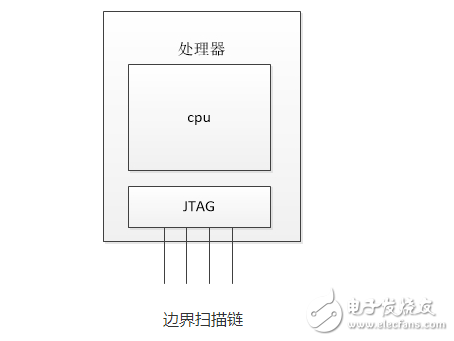

在CPU外围,处理器内部包含了JTAG的硬件实现,并且向外界提供接口,也就是上面所说的TMS、TCK、TDI、TDO四个引脚。

这里的CPU:是指运算处理单元,只包含了内部寄存器以及运算单元等基本部件。

这里的处理器:是指CPU 扩展芯片,不是SoC。

JTAG如何用于芯片测试呢? 其中用到的最主要部件就是边界扫描链。命名为边界扫描链,是由于它位置处于处理器的边界上。

我们知道CPU是通过引脚与外围交流的,所有的数据都会通过引脚输入或者输出,而JTAG就是通过监控引脚的信号达到芯片测试的目的。而边界扫描链就是在引脚上的一个部件。如下图:

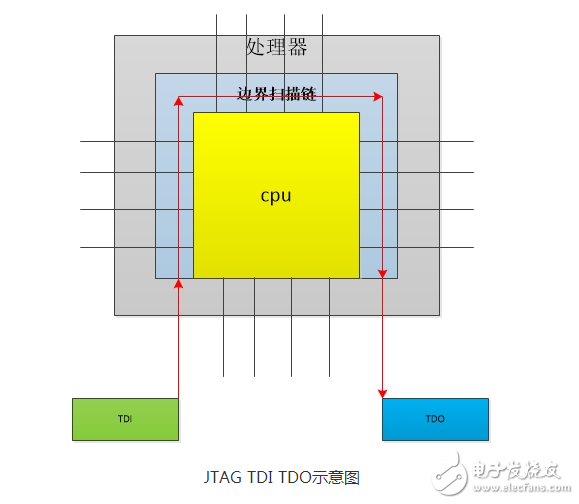

通过边界扫描链,当有信号输入的时候,边界扫描链就能获取信号,当CPU要输出信号的时候,边界扫描链也能获取要输出的信号。另外,也可以通过边界扫描链来直接向外部输出信号。

无论是信号的抓取还是输出,都需要有接口来保存这些信号,TDI 跟 TDO 就是做这样一些工作的。如图:

本来边界扫描链保存着引脚上的信号,当通过TDI引脚输入我们自己的信号的时候,会发生沿上面红线方向的移位 *** 作,

TDI ——〉 边界扫描链 —— 〉 TDO

就能从TDO获取边界扫描链上的信号,我们从TDI输入的信号也会到边界扫描链上去。

在CPU跟外界通信的引脚上的数据无非就是 指令 跟 数据信号(包括地址跟数据) 两种。但是这两者的结合形成了一个完整的程序,能对它们进行监控就表明我们能进行程序的调试。一般的芯片都会提供几条独立的边界扫描链,对边界扫描链的控制主要是通过 TAP(Test Access Port) Controller来完成的。

上面的只是jtag最基本的原理,要对程序更好的调试还需要控制部件,还有更多寄存器的结合等等。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)