使用寿命预测指标

功率GaN落后于RF GaN的主要原因在于需要花时间执行数个供货商所使用的成本缩减策略。最知名的就是改用6英寸的硅基板,以及更低成本的塑料封装。对于电源设计人员来说,理解GaN有可能带来的性能提升,以及某些会随时间影响到最终产品性能的退化机制很重要。

联合电子设备工程委员会 (JEDEC) 针对硅器件的认证标准经证明是产品使用寿命的很好预测指标,不过目前还没有针对GaN的同等标准。要使用全新的技术来减轻风险,比较谨慎的做法是看一看特定的用例,以及新技术在应用方面的环境限制,并且建立能够针对环境变化进行应力测试和监视的原型机。对于大量原型机的实时监视会提出一些有意思的挑战,特别是在GaN器件电压接近1000V,并且dv/dts大于200V/ns时更是如此。

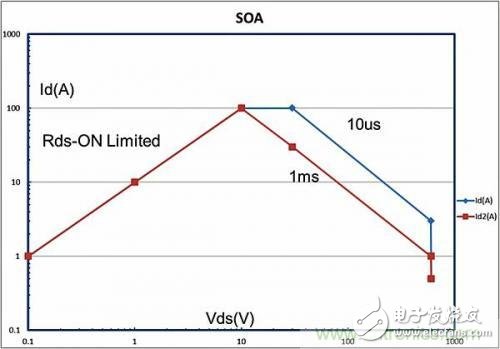

一个经常用来确定功率FET是否能够满足目标应用要求的图表是安全工作区域 (SOA) 曲线。图1中显示了一个示例。

图1.GaN FET SOA曲线示例,此时Rds-On = 毫欧

硬开关设计

功率GaN FET被用在硬开关和数MHz的谐振设计中。上面展示的零电压 (ZVS) 或者零电流 (ZCS) 拓扑为数千瓦。SOA曲线的应力最大的区域是右上角的电压和电流最高的区域。在这个硬开关区域内运行一个功率GaN FET会导致由数个机制而造成的应力增加。最容易理解的就是热应力。例如,在使用一个电感开关测试电路时,有可能使器件从关闭时的电流几乎为零、汲取电压为几百伏,切换到接通时的电流几乎瞬时达到10A。

器件上的电压乘以流经的电流可以获得瞬时功率耗散,对于这个示例来说,在转换中期可以达到500W以上。对于尺寸为5mm x 2mm的典型功率GaN器件,这个值可以达到每mm2 50W。所以用户也就无需对SOA曲线显示的这个区域只支持短脉冲这一点而感到惊讶了。由于器件的热限值和封装的原因,SOA曲线的右上部被看成是一个脉宽的函数。由于曲线中所见的热时间常数,更短的脉冲会导致更少的散热。增强型封装技术可被用来将结至环境的热阻从大约15°C/W减小到1.2°C/W。由于减少了器件散热,这一方法可以扩大SOA。

SOA曲线

TI有一个系列的标准占板面积的功率MOSFET、DualCool™ 和NexFETs™。这些MOSFET通过它们封装顶部和底部散热,并且能够提供比传统占板面积封装高50%的电流。这使得设计人员能够灵活地使用更高电流,而又无需增加终端设备尺寸。与硅FET相比,GaN FET的一个巨大优势就是可以实现的极短开关时间。此外,减少的电容值和可以忽略不计的Qrr使得开关损耗低很多。在器件开关时,电压乘以电流所得值的整数部分是器件必须消耗的功率。更低的损耗意味着更低的器件温度和更大的SOA。

SOA曲线所圈出的另外一个重要区域受到Rds-On的限制。在这个区域内,器件上的电压就是流经器件的电流乘以导通电阻。在图1所示的SOA曲线示例中,Rds-On为100毫欧。硅MOSFET的温度取决于它们的Rds-On,这一点众所周知。在器件温度从25ºC升高至大约100ºC时,它们的Rds-On几乎会加倍。

动态Rds-On

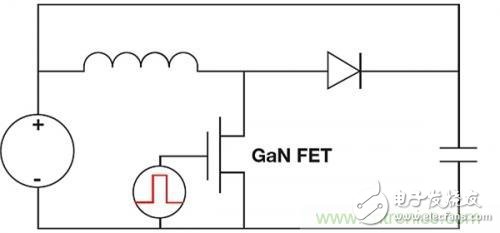

GaN FET具有一个复杂的Rds-On,它是温度,以及电压和时间的函数。GaN FET的Rds-On对电压和时间的函数依赖性被称为动态Rds-On。为了预测一个GaN器件针对目标使用的运行方式,很有必要监视这些动态Rds-On所带来的影响。与SOA曲线的温度引入应力相类似,电感硬开关应力电路比较适合于监视Rds-On。这是因为很多潜在的器件退化是与高频开关和电场相关的。

图2是一个简单开关电路,这个电路中给出了一种在SOA右上象限内实现循环电流,并对器件施加应力的方法。

图2.电感硬开关测试电路

宽带隙

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)