如于2016年1月1日生效的欧盟CoC V5 TIer 2 规定,输出功率为45 W和65 W的AC-DC适配器平均能效需分别达到87.7%和89%,待机功耗分别低于75 mW和150 mW,并且还要求10%负载条件时的能效需分别达到77.7%和77.5%。电源设计工程师面临体积、能效和成本等多方面的设计挑战。

表1. AC-DC 适配器能效法规一览

开关频率直接决定开关电源的功率密度,提高开关频率可有效地减小无源功率器件如变压器、输出电容的尺寸,从而提高功率密度;高功率密度应用仅满足能效规范远远不够,因为体积减小时,散热面积也相应减少,需提高能效以减少发热,减小对内部元器件寿命的影响;此外,工程师需将成本控制在合理范围内,以在竞争激烈的市场处于有利地位。

准谐振反激 + 同步整流 = 高功率密度适配器

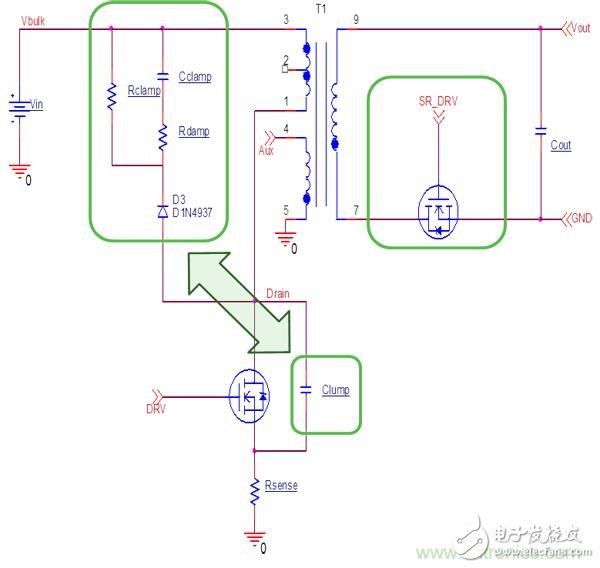

LLC拓扑结构可提供高频率和高能效,但其成本较高,且对输入电压范围有严格要求,不适用于笔记本电脑这一功率等级。采用准谐振反激式拓扑加上同步整流(SR)可轻松地设计出满足体积、能效、成本等要求的高功率密度适配器,如安森美半导体的高频准谐振反激式控制器NCP1340/1+SR控制IC NCP4305/80。

准谐振模式允许使用相对大的缓冲电容Clump,额外增加的Clump (10-22pF)可以减少MOS管关断损耗,减少电磁干扰(EMI)。准谐振反激有利于次极端加SR,可降低整流二极管导通损耗,减少次极端整流管尖峰电压,降低其耐压要求。

图1. 准谐振模式允许使用相对大的缓冲电容Clump

准谐振式反激电源损耗分析和设计要点

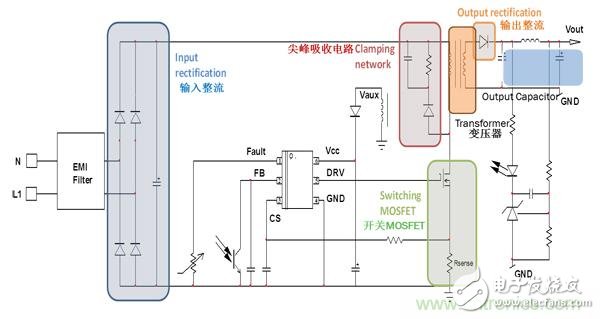

分析准谐振反激损耗旨在提高工作频率后再减少功率损耗。准谐振反激电源的损耗主要分布在初级MOSFET、尖峰吸收电路、变压器和输出整流。

图2. 准谐振反激电源的损耗分布

1.初级MOSFET损耗分析

初级MOSFET损耗主要包括导通损耗、开关损耗和驱动损耗。导通损耗由漏源导通阻抗Rds(on)和初级端均方根电流定义。对于开关损耗,由于MOSFET的结电容与其Vds电压成非线性比例,所以不能用简单的电容储能公式计算,需要将实际的结电容考虑进去,结电容可理解为MOSFET DS 网络间等效的除了MOSFET内部的结电容外的其它电容。驱动损耗在开关频率较低时可以不作考虑,但在高频应用中不能忽略,它在MOSFET导通和关断时产生,主要取决于MOSFET总门极电荷Qg、开关频率和IC工作电压Vcc,损耗大部分消耗在驱动电阻上。

因此,对于MOSFET的选取,在高频应用中,Rds (on) x Qg乘积数越低越有利于降低导通损耗和驱动损耗。应选择体积小、薄且散热性好的低热阻封装。由于氮化镓(GaN) MOSFET具有更优的Rds (on) x Qg参数,可额外增加约0.3%的满载效率,而在成本允许的情况下,GaN MOSFET是理想的选择。

2. 尖峰吸收电路损耗分析

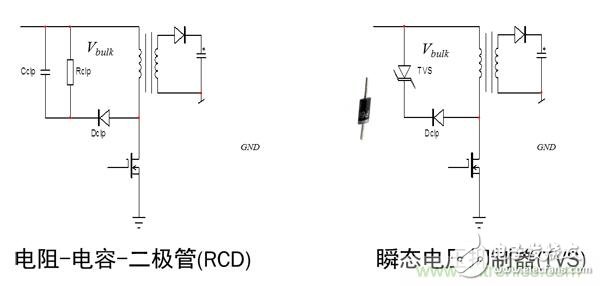

尖峰吸收电路主要用于钳制MOS管Vds电压,防止其过压击穿。电阻-电容-二极管(RCD)吸收和瞬态电压抑制器(TVS)吸收是两种常用的电路,其中RCD最为常用,可靠性较高。

图3. 两种常见的尖峰吸收电路

对于RCD电路中,较大的吸收电容C可减少钳位电压纹波,但会增加待机功耗,所以C的选取一般以满载时5%至10%钳位电压纹波为宜。如果吸收电阻R较热,可减小变压器漏电感,选用Trr一致性好的慢管,可降低钳位电压,减少R损耗。

钳位电压方面,选择高的钳位电压可降低RCD吸收损耗,但需选高耐压MOS管,这会导致成本增加,而且变压器初级电流衰减速度会变快,次级整流电流上升斜率变陡,不利于EMI和次级同步整流效率优化。选择低的钳位电压,有利于EMI,次级同步整流控制,但RCD吸收损耗会增加。整流二极管D选用慢管可减少钳位电压和改善EMI,但二极管温升会较高。所以需综合考虑各方面影响,权衡择取。

3. 变压器损耗分析

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)