在应用电源模块常见的问题中,降低负载端的纹波噪声是大多数用户都关心的。下文结合纹波噪声的波形、测试方式,从电源设计及外围电路的角度出发,阐述几种有效降低输出纹波噪声的方法。

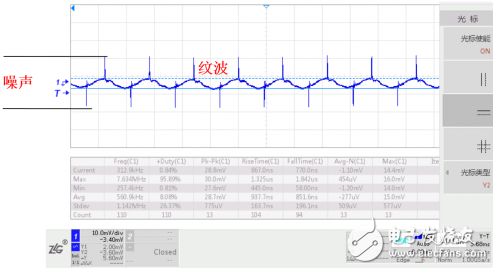

1、电源的纹波与噪声图示

纹波和噪声即:直流电源输出上叠加的与电源开关频率同频的波动为纹波,高频杂音为噪声。具体如图1所示,频率较低且有规律的波动为纹波,尖峰部分为噪声。

2、纹波噪声的测试方法

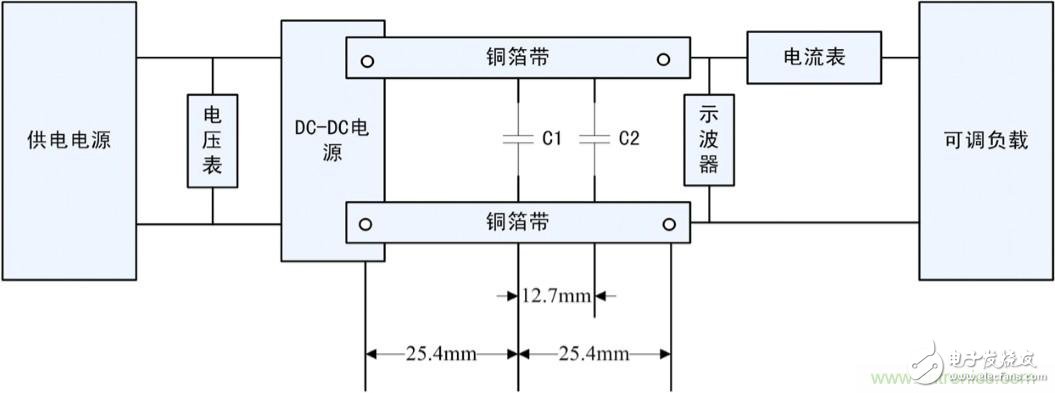

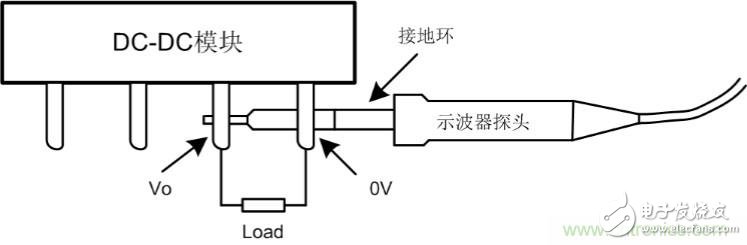

对于中小微功率模块电源的纹波噪声测试,业内主要采用平行线测试法和靠接法两种。其中,平行线测试法用于引脚间距相对较大的产品,靠测法用于模块引脚间距小的产品。

但不管用平行线测试法还是靠测法,都需要限制示波器的带宽为20MHz,同时需要去掉地线夹。

具体如图2和图3所示。

图2 平行线测试法

注1:C1为高频电容,容量为1μF;C2为钽电容,容量为10μF。

注2:两平行铜箔带之间的距离为2.5mm,两平行铜箔带的电压降之和应小于输出电压的2%。

图3靠测法

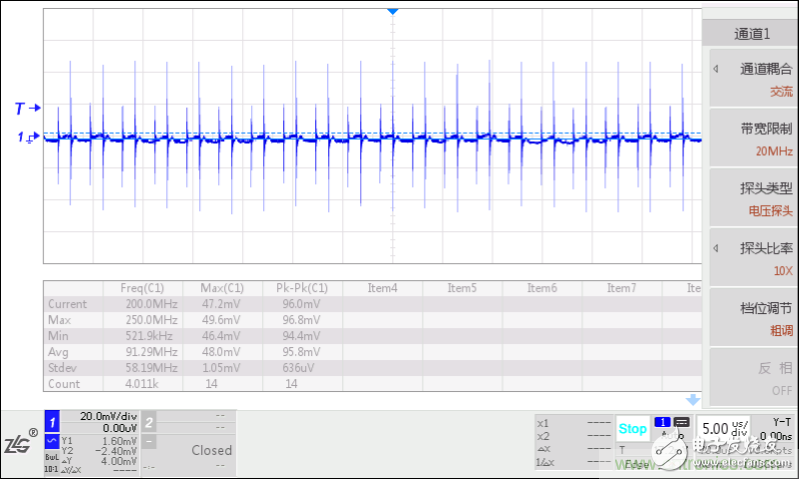

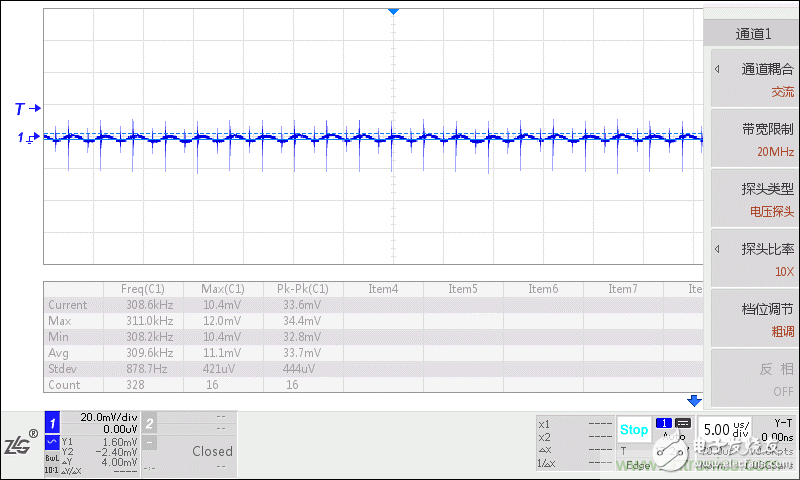

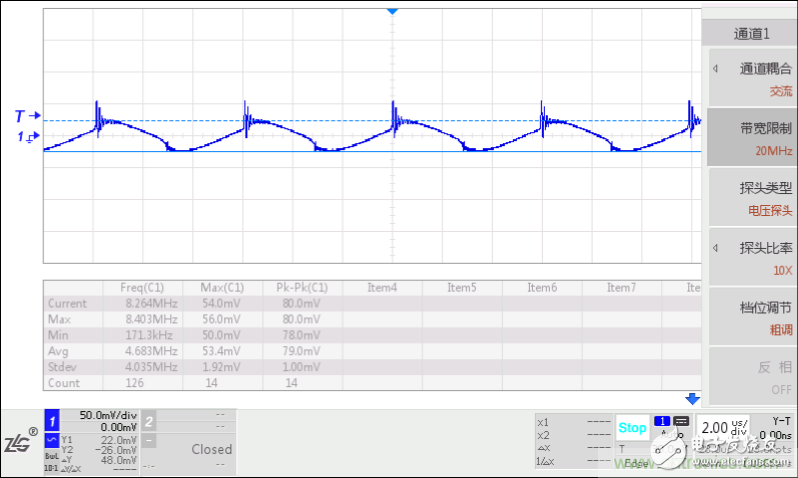

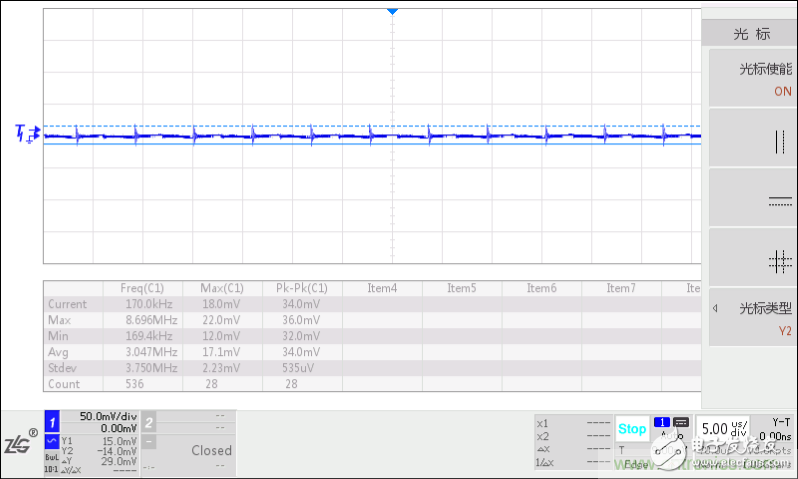

3、去除地线夹测试的区别

测试纹波噪声需要把地线夹去掉,主要是由于示波器的地线夹会吸收各种高频噪声,不能真实反映电源的输出纹波噪声,影响测量结果。下面的图4和图5分别展示了对同一个产品,使用地线夹及取下地线夹测试的巨大差异。

图4 使用地线夹测试-示波器垂直分辨率200mv/div

图5 去除地线夹测试-示波器垂直分辨率50mv/div

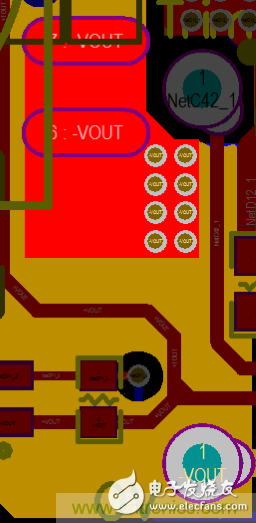

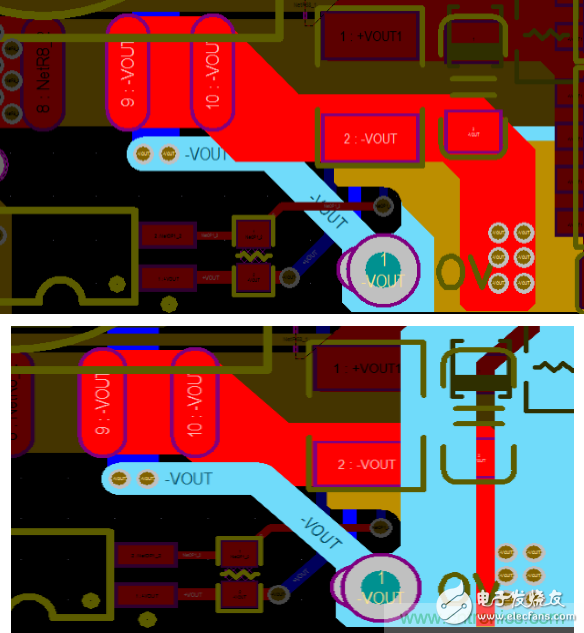

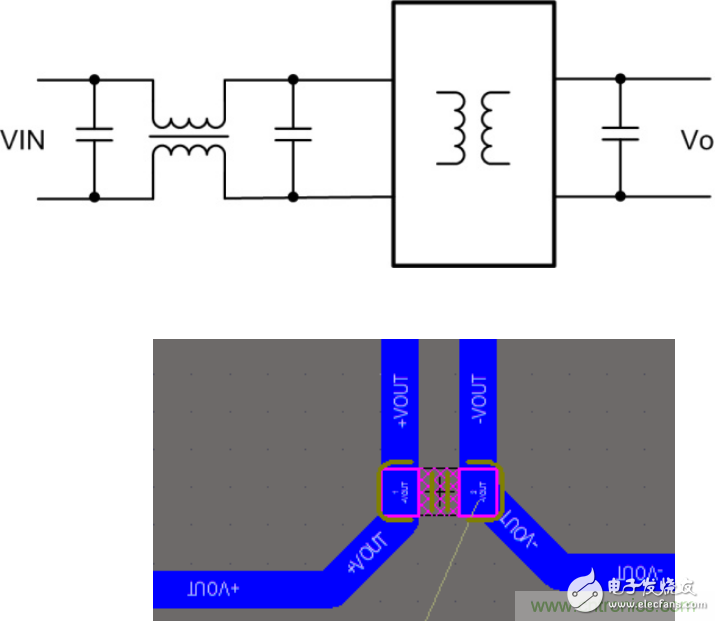

4、设计上PCB布局的影响

好与坏的PCB布局,是设计上影响纹波噪声的关键因素。差的PCB布局如图6所示,变压器输出的地,直接通过过孔连到背部的地平面,地平面连接电源的输出引脚。此布局在输出5V/2A的负载下,实测电源尖峰达1.5V VP-P。

图6 差的PCB布局

如图7 所示是比较好的PCB布局,调整了变压器的位置,将变压器输出地通过两个电容后,再回到地平面和输出引脚相连。实测在相同5V/2A输出的负载下,噪声已降到60mV VP-P,差别显著。

图7 好的PCB布局

5、输出滤波电容的影响

输出滤波电容的容值、ESR对模块输出的纹波噪声也有直接影响。按图8所示的 产品测试纹波噪声。

外部不加外接电容,测试输出的纹波噪声,如图图9所示,约为100mV。同样的输入、负载条件下,电源的输出端加226的MLCC,实测电源输出的纹波噪声降到不到40mV。

图8 测试用图

图9 无外接电容

图10 外加226电容

实际应用时,电容除容量、ESR外,建议负载端的电容在回到电源之前,先汇集到输出电容,经过电容滤波后,再回到电源,从而有效降低纹波噪声对电路的影响。如图11所示。

图11 外部电容的位置

6、电感对纹波噪声的影响

电感的感量及寄生电容对纹波噪声的影响同样显著。一般地,感量大时对纹波抑制作用明显,寄生电容小的电感对噪声抑制效果好。以对纹波抑制为例,测试对电源输出纹波的影响,测试图如图12所示。

图12 测试电感滤波效果用例

根据图12,我们先人为的把产品内部的滤波电感短路,只用电容滤波,测得纹波噪声如图13所示,纹波峰峰值约50mV。

图13 人为短路内部滤波电感的纹波噪声图

下一步,在电源外部增加一个LC电路,在相同输入、负载条件下,重测纹波噪声图,如图14所示,纹波已接近直线,非常小。

图14 外加LC的纹波噪声图

以上简单从纹波噪声的图例、测试方法开始,描述从电源设计、外部电路应用出发,结合实际测试比较几种降低纹波噪声的方法。实际的工程应用中还需考虑电容、电感的负载效应、自激影响等,还需再做深究。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)