本篇文章来自赛灵思高级工具产品应用工程师 Hong Han

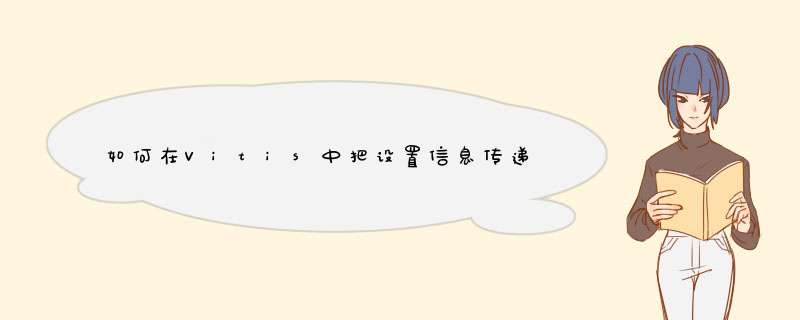

在ViTIs 统一软件平台中使用v++ -link命令,可以把各种类型Kernel(C, C++, OpenCL™ C, 以及 RTL)的对象文件(.XO)整合到目标平台中,最终生成器件的二进制文件XCLBIN

在ViTIs完成这个过程的底层,实际调用的是Vivado。ViTIs会指定默认的Vivado策略来执行综合和实现的步骤。当默认的Vivado策略无法达到预期的时序要求时,我们需要在Vivado中分析时序问题的原因(不在本篇中详细讨论), 并根据时序失败的原因调整Vivado各个步骤的选项。有时我们也需要调整Vivado各个步骤的选项做不同方向的优化.

在ViTIs中提供了"--vivado" 选项来精细控制Vivado各个步骤的选项,几乎所有期望加在Vivado中的选项都可以通过这个选项传递给Vivado。以下 *** 作如何选择合适的选项需要对于Vivado的运行机制有一定的了解,对于Vivado不熟悉的用户,建议先阅读UG901以及UG904,两者分别是综合和实现的使用手册

1. 对于应用于Vivado的参数使用选项:

--vivado.param =

举例:

--vivado.param project.writeIntermediateCheckpoints=1

对应Vivado中参数设置的命令:

set_param project.writeIntermediateCheckpoints

这个命令也可以放在Vivado各个阶段的TCL.PRE/TCL.POST所指定的脚本中用--vivado.prop 执行(参考"Vivado工程的属性设置"的内容)

对应configure文件的内容:

[vivado] param=project.writeIntermediateCheckpoints=1

2. 对于Vivado工程的属性设置:

--vivado.prop . .

这里的Object_type是可以是run, fileset, file 或者 project

举例:

v++ --link --vivado.prop run.impl_1.STEPS.PHYS_OPT_DESIGN.IS_ENABLED=true --vivado.prop run.impl_1.STEPS.PHYS_OPT_DESIGN.ARGS.DIRECTIVE=Explore --vivado.prop run.impl_1.STEPS.PLACE_DESIGN.TCL.PRE=/…/xxx.tcl

指定了在Vivado 实现阶段执行PHYS_OPT_DESIGN步骤

(注:Vivado中PHYS_OPT_DESIGN步骤默认并不执行)

指定了在PHYS_OPT_DESIGN步骤采用的directive 是 Explore

指定了在Place_design之前需要先执行一个tcl脚本.

对应configure文件的内容:

[vivado] prop=run.impl_1.steps.phys_opt_design.is_enabled=1 prop=run.impl_1.STEPS.PHYS_OPT_DESIGN.ARGS.DIRECTIVE=Explore prop=run.impl_1.STEPS.PLACE_DESIGN.TCL.PRE=/…/xxx.tcl

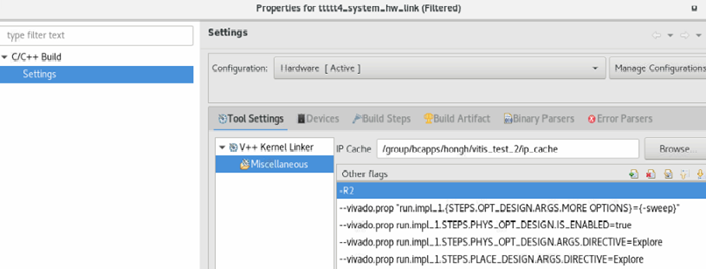

不少Vivado实现阶段的选项无法直接在Vivado工程模式的各个阶段的既有选项中直接体现,例如在opt_design 阶段,我只想执行 -sweep 选项,这时我们可以用到这些步骤的"More Option"

opt_design -sweep 相当于在在工程模式中设置opt_design的More option 为 -sweep

由于"More Option" 这个选项中含有空格,使用起来要相当小心。一旦用错,这个选项在v++中可能和其他的选项混淆,导致工具报一些看似无关的错误

示例:

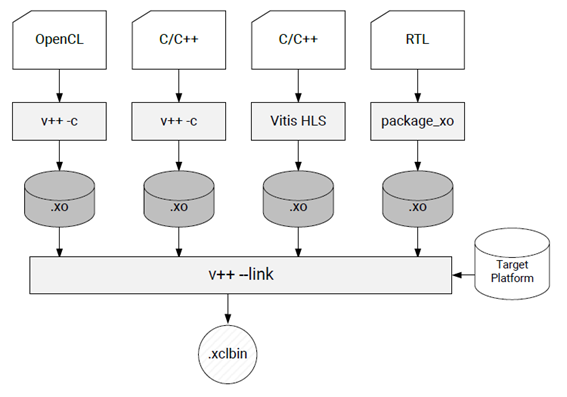

--vivado.prop "run.impl_1.{STEPS.OPT_DESIGN.ARGS.MORE OPTIONS}={-sweep}"

我们先将Vivado的相关属性加到Vitis link的选项中

完成Vitis platform link之后,打开生成的Vivado 工程,我们可以看到之前设置的Vivado 属性都能体现在底层Vivado工程中:

(Vivado工程文件所在目录(不同版本可能有所差异):

XX/XX_system_hw_link/Hardware/binary_container_1.build/link/vivado/vpl/prj/prj.xpr)

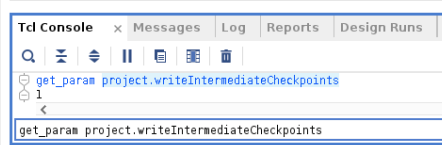

在Vivado 的TCL CONSOLE中可以执行get _param命令查看parameter是否已经设置成功:

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)