信号发生器用来产生确定性电信号,其特性随时间推移而变化。如果这些信号表现为简单的周期性波形,如正弦波、方波或三角波,那么这种信号发生器就称为函数发生器。它们通常用于检查电路或PCBA的功能。将确定性信号加到被测电路的输入端,将输出端连接至相应的测量设备(例如示波器),用户就可以对其进行评估。过去,挑战通常包括如何设计信号发生器的输出级。本文将介绍如何利用电压增益放大器(VGA)和电流反馈放大器(CFA)设计小型经济的输出级。

典型的信号发生器可提供25mV至5V输出电压。为了驱动50Ω或更高的负载,一般会在输出端使用大功率分立器件、多个并行器件,或者成本高昂的ASIC。其内部通常具有继电器,可以使设备在不同的放大或衰减等级之间进行切换,从而调节输出电平。根据需要,在对继电器开关而实现各种增益时,在一定程度上会导致工作不连续。简化方框图如图1所示。

图1:典型信号发生器输出级的简化方框图。

使用新款放大器IC作为输出级功放,可以在没有任何内部继电器的情况下直接驱动负载,因此可简化信号发生器的输出级设计,并降低复杂度和成本。这种输出的两个主要器件构成一个大功率输出级,可提供高速、高电压和大电流,以及具有连续线性微调功能的可变放大器。

图2.带VGA的信号发生器输出级的简化框图

首先,初始输入信号必须通过VGA放大或衰减。VGA的输出信号可以设置为所需的幅度,而与输入信号无关。例如,对于增益为10、输出幅度VOUT为2V的情况,VGA的输出幅度必须调整至0.2V。遗憾的是,许多VGA都会因为增益范围有限而产生瓶颈——增益范围大于45dB的情况很少。

ADI公司在低功耗VGA AD8338上实现了0dB至80dB可编程增益范围。因此,在理想条件下,可以将信号发生器的输出幅度连续设置在0.5mV和5V之间,而无需使用额外的继电器或开关网络。通过去除这些机械元件,可以避免不连续的输出。因为数模转换器(DAC)和直接数字频率合成器(DDS)通常具有差分输出,所以AD8338提供全差分接口。此外,通过灵活的输入级,输入电流有任何的不对称,都可以通过内部反馈回路得到补偿。同时,内部节点保持在1.5V。在正常情况下,最大1.5V输入信号在500Ω输入电阻时会产生3mA电流。在更高输入幅度(例如15V)的情况下,可能需要在输入引脚串联一个更大的电阻——其阻值要确保所产生的电流同样为3mA大小。

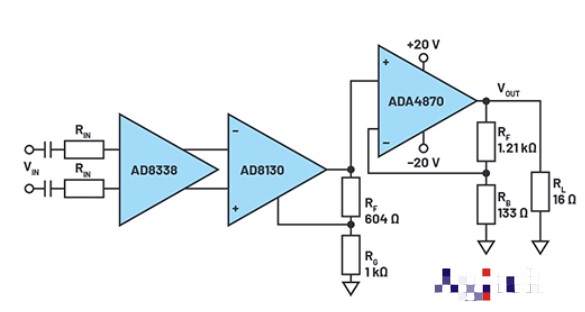

许多商用信号发生器在50Ω(正弦波)负载下提供最大250mW(24dBm)的有效输出功率。但是,这对于具有较大输出功率的应用通常不够用,例如测试HF放大器或生成超声波脉冲之所需。因此,还需要使用电流反馈放大器。ADA4870在±20V电源电压下,可以在输出端以17V的幅度提供1A的驱动电流。它可以在满载情况下生成高达23MHz的正弦波,因此成为了通用任意波形发生器的理想前端驱动器。为了优化输出信号摆幅,ADA4870的增益配置成10,因此所需的输入幅度为1.6V。但是,由于ADA4870具有地参考输入,而上游的AD8338具有差分输出,因此在两个器件之间应连接差分接收器放大器,而实现差分到地参考的转换。AD8130提供270MHz的增益带宽积(GBWP),压摆率为1090V/µs,非常适合这种应用。AD8338的输出限制在±1V,因此AD8130的中间增益应设计为1.6V/V。整体电路配置如图3所示,其可在22.4V(39dBm)幅度和50Ω负载下实现20MHz带宽。

图3:采用分立设计的信号发生器输出级的简化电路。

通过大功率的VGA(AD8338)、大功率的CFA(ADA4870)和差分接收器放大器(AD8130)的组合,就可以相对轻松地设计出小尺寸大功率的信号发生器输出级。它具有更高的系统可靠性、更长的服务寿命和更低的成本,因此比传统输出级更优。

审核编辑:刘清

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)