一前言

相信诸位研发工程师对EMC这个词并不陌生,但是怎么做到让EMC风险最小,却是十分头疼的问题。对于了解EMC是什么,知道怎么处理EMC的工程师来说,PCB板的EMC风险评估并没有想象中的那么困难。可以简单的分为三大步来看。

二了解产品特性

在设计初期,研发工程师除了考虑产品的基础功能外,还需要对PCB板与外壳之间的结构关系,以及金属端口与外壳之间的连接关系。方便前期原理图设计与PCB布局的时候,提前将需要注意的“接地点”或者“漏铜”等预留措施设计进去,避免后期二次改板。例如:金属外壳的产品,PCB板固定的时候,螺丝孔是否需要漏铜,将外壳与PCB板的GND连接到一起的作用,金属端口是直接与金属外壳靠结构上的缝隙进行连接,还是靠辅助材料进行一个连接?

这都是一个研发工程师在前期设计时,需要考虑的一个问题,而不是等结构那边做完结构以后,再去反馈的问题!了解整个产品的特性,会让研发工程师在开拓自己边界的同时,也会将诸多隐患问题也考虑进去,避免后期的二次改动和结构变化。

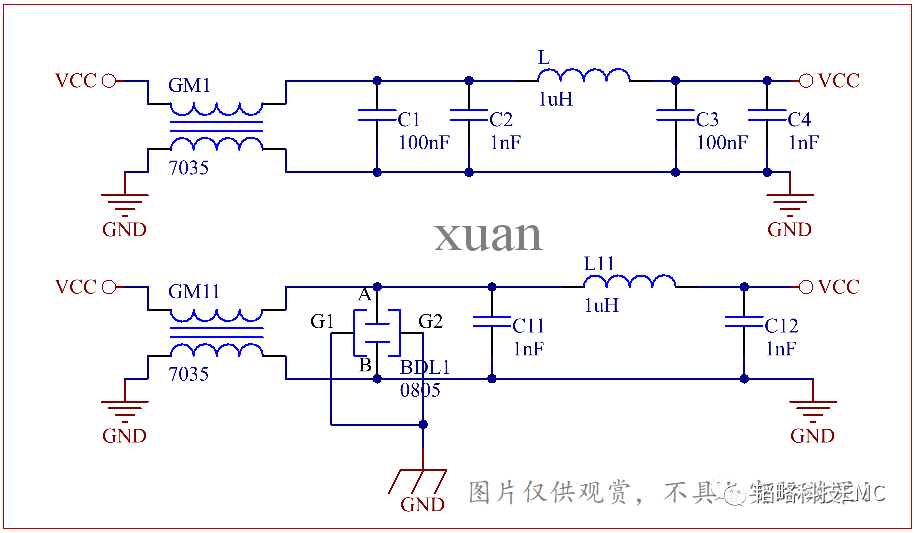

三原理图设计

在部分小公司里面,对原理图的设计缺少专业的审核,能实现基本功能满足要求即可,从而忽视了原理图设计阶段的“风险评估”。例如:产品的静电抗扰度,传导发射辐射,耐压测试等等一些测试项目,他们需要的措施都各不相同,原理图设计前期不做考虑,会导致后期测试不通过,而进行二次设计,这样会浪费很多时间和资源。

但是,在原理图设计的初期,怎样去评估和评判原理图需要做哪些设计呢?其实,只要根据现有项目的项目要求中提到的功能,测试项目等一些标准文件去进行设计,可以很大程度上避免后期的原理图二次设计的麻烦。

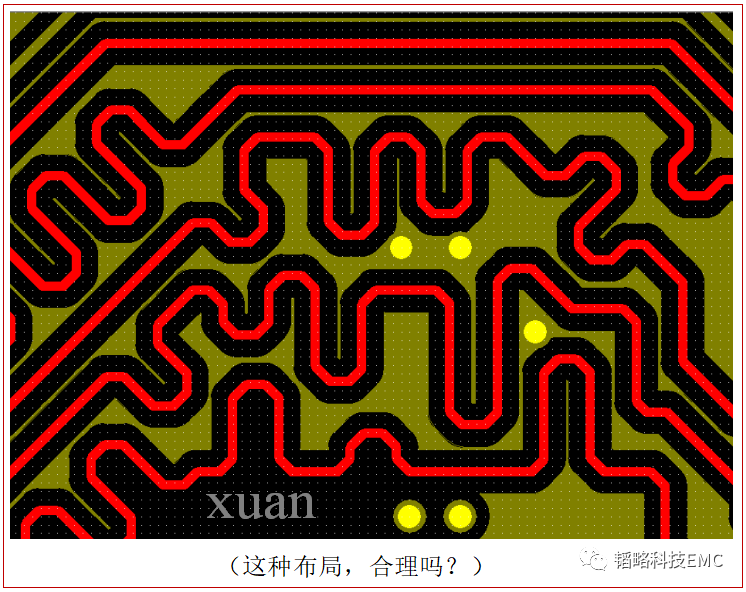

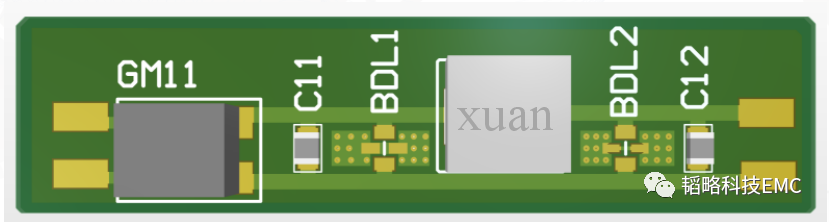

四PCB布局设计

虽然,原理图的设计很重要,但是对于EMC和安规的部分高压测试项来说,PCB的布局和走线更是关键。有句硬件工程师都很熟悉的话“能用布局走线解决的问题,就不要额外增加器件!”因为PCB的布局走线好坏真的就直接影响了产品测试通过率,而怎样的PCB布局就是好的?怎样的PCB布局就是差的?

需要注意的是,在进行PCB布局的时候,需要对重要的、敏感的信号进行优先布局,而且布局必须按照布局规则进行。其次对于电源和高压部分单独布局,不要与其他低压、敏感信号走线过于靠近,这些规则网络上也有很多,这里就不过多进行描述。

PCB工程师在设计完PCB布局以后,最好再仔细复查一遍,看看有没有什么不合理的地方与布局不正确的地方,最后再由资深老工程师进行审核,看看需要做预留与预处理的地方是否都已完成!

五总结

EMC的风险评估,说简单也简单,说复杂也复杂。关键还是对产品的了解是否透彻,对原理图设计与PCB布局是否注重细节,熟悉项目要求!

审核编辑:汤梓红

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)