虽然在技术上仍然是新事物,但用于主机到设备连接的 Compute Express Link (CXL) 标准已迅速在服务器市场占据一席之地。

据报道,该标准旨在提供建立在现有 PCI-Express 标准之上更丰富的 I/O 功能集,其最显著的是优势在于设备之间的缓存一致性。从相关组织处获悉,CXL的主要应用方向是把CPU连接到服务器中的加速,但希望能够在物理上仍然是通过 PCIe 接口上连接 DRAM 和非易失性存储。

这是一个雄心勃勃但得到广泛支持的路线图,在短短三年内使,CXL 便成为事实上的先进设备互连标准,这就导致竞争对手标准 Gen-Z、CCIX 以及截至昨天的 OpenCAPI 都退出了竞争。

虽然 CXL 联盟在赢得互连战争后快速取得胜利,但联盟及其成员还有很多工作要做。假如在产品方面,第一批带有 CXL 的 x86 CPU 几乎没有出货——这很大程度上取决于你所说的英特尔 Sapphire Ridge 芯片所处的边缘状态。

来到功能方面,设备供应商要求获得比比 CXL 的原始 1.x 版本更多的带宽和更多的功能。赢得互连战争使 CXL 成为互连之王,但在此过程中,这意味着 CXL 需要能够解决竞争对手标准设计的一些更复杂的用例。

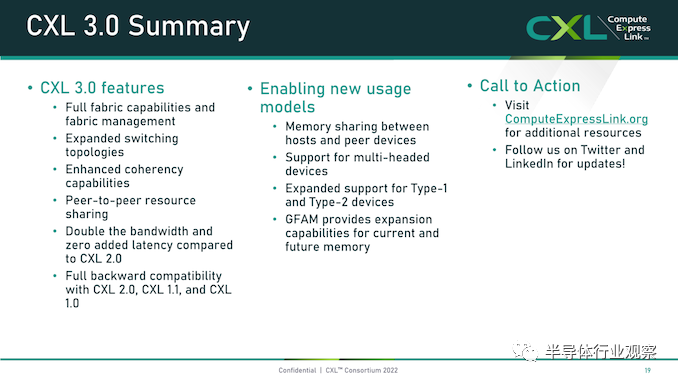

为此,在本周的 2022 年闪存峰会上,CXL 联盟在展会上宣布了 CXL 标准的下一个完整版本 CXL 3.0。这是继2020 年底发布 2.0 标准并引入了内存池和 CXL 开关等功能之后的一次重要更新。

报道指出,CXL 3.0 侧重于互连的几个关键领域的重大改进。第一个是物理方面,CXL 将其每通道吞吐量翻了一番,达到 64 GT/秒。同时,在逻辑方面,CXL 3.0 大大扩展了标准的逻辑能力,允许复杂的连接拓扑和结构,以及在一组 CXL 设备内更灵活的内存共享和内存访问模式。

CXL 3.0:建立在 PCI-Express 6.0 之上

首先,我们从物理方面开始了解新版本的CXL 技术。资料显示,新版本的标准提供了期待已久的更新,以合并 PCIe 6.0。CXL 之前的两个版本,也就是 1.x 和 2.0,都是建立在 PCIe 5.0 之上的,所以这是自 2019 年 CXL 推出以来,其物理层的首次更新。 PCIe 6.0本身是对 PCI-Express 标准内部工作的重大更新,它再次将总线上的可用带宽量翻了一番,达到 64 GT/秒,对于 x16 卡来说,这可以达到 128GB/秒。据报道,这个速度是通过将 PCIe 从使用二进制 (NRZ) 信号转换为四态 (PAM4) 信号并结合固定数据包 (FLIT) 接口来实现的。借助这种方法,能使其速度翻倍而不会在更高频率下运行的缺点。由于 CXL 反过来构建在 PCIe 之上,这意味着需要更新标准以应对 PCIe 的 *** 作变化。

CXL 3.0 的最终结果是它继承了 PCIe 6.0 的全部带宽改进——以及前向纠错 (FEC) 等所有有趣的东西——与 CXL 2.0 相比,CXL 的总带宽增加了一倍。 值得注意的是,根据 CXL 联盟的说法,他们能够在不增加延迟的情况下完成所有这些工作。这是 PCI-SIG 在设计 PCIe 6.0 时面临的挑战之一,因为必要的纠错会增加进程的延迟,导致 PCI-SIG 使用低延迟形式的 FEC。尽管如此,CXL 3.0 在尝试减少延迟方面更进了一步,导致 3.0 具有与 CXL 1.x/2.0 相同的延迟。 除了基本的 PCIe .60 更新之外,CXL 联盟还调整了他们的 FLIT size。CXL 1.x/2.0 使用了一个相对较小的 68 字节数据包,而 CXL 3.0 将其增加到了 256 字节。更大的 FLIT size是 CXL 3.0 的关键通信变化之一,因为它在header FLIT 中为标准提供了更多位,而这些位又是启用 3.0 标准引入的复杂拓扑和结构所必需的。尽管作为一项附加功能,CXL 3.0 还提供了一种低延迟“变体”FLIT 模式,该模式将 CRC 分解为 128 字节“sub-FLIT granular transfers”,旨在减轻物理层中的存储和转发开销. 值得注意的是,256 字节的 FLIT 大小使 CXL 3.0 与 PCIe 6.0 保持一致,后者本身使用 256 字节的 FLIT。和它的底层物理层一样,CXL 不仅支持在新的 64 GT/秒传输速率下使用大型 FLIT,而且还支持 32、16 和 8 GT/秒,本质上允许新协议功能以更慢的传输速率使用. 最后,CXL 3.0 完全向后兼容早期版本的 CXL。因此,设备和主机可以根据需要降级以匹配硬件链的其余部分,尽管在此过程中会失去更新的功能和速度。

CXL 3.0 特性:增强的一致性、

内存共享、多级拓扑和结构

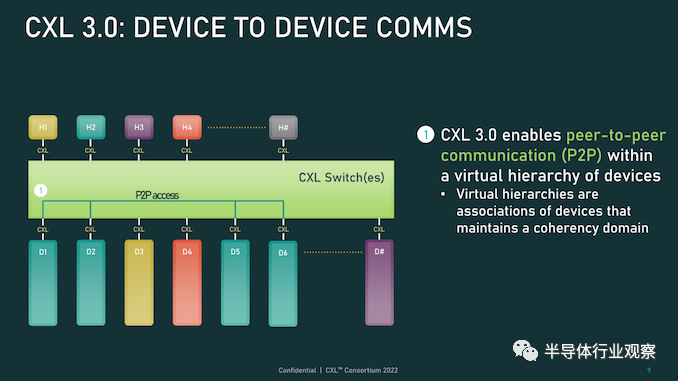

除了进一步提高整体 I/O 带宽外,上述针对 CXL 的协议更改也已实施,以支持标准内的新功能。CXL 1.x 是作为(相对)简单的主机到设备标准而诞生的,但现在 CXL 是服务器的主要设备互连协议,它需要扩展其功能以适应更高级的设备,并最终适应更大的用例。 从特性级别开始,这里最大的新闻是该标准更新了具有内存的设备的缓存一致性协议(Type-2 和 Type-3,用 CXL 的说法)。正如 CXL 所说,增强的一致性允许设备支持使主机缓存的数据无效。这取代了 CXL 早期版本中使用的基于偏差的一致性方法,为了保持简洁,保持一致性不是通过共享内存空间的控制,而是通过让主机或设备负责控制访问。相比之下,Back invalidaTIon更接近真正的共享/对称方法,允许 CXL 设备在设备进行更改时通知主机。 包含Back invalidaTIon也为设备之间的新对等连接打开了大门。在 CXL 3.0 中,设备现在可以直接访问彼此的内存,而无需通过主机,使用增强的一致性语义来通知彼此它们的状态。从延迟的角度来看,跳过主机不仅速度更快,而且在涉及交换机的设置中,这意味着设备不会通过请求占用宝贵的主机到交换机带宽。虽然我们稍后会进入拓扑,但这些变化与更大的拓扑密切相关,允许将设备组织成虚拟层次结构,其中层次结构中的所有设备共享一个一致性域。

除了调整缓存功能外,CXL 3.0 还对主机和设备之间的内存共享进行了一些重要更新。CXL 2.0 提供了内存池,其中多个主机可以访问设备的内存,但必须为每个主机分配自己的专用内存段,而 CXL 3.0 引入了真正的内存共享。利用新的增强一致性语义,多个主机可以拥有一个共享段的一致副本,如果设备级别发生变化,可以使用反向失效来保持所有主机同步。

然而,应该注意的是,这并不能完全取代池化。在某些用例中,CXL 2.0 风格的池更可取(保持一致性需要权衡取舍),并且 CXL 3.0 支持根据需要混合和匹配这两种模式。 CXL 3.0 进一步增强了这种改进的主机设备功能,消除了之前对可以连接到单个 CXL 根端口下游的 Type-1/Type-2 设备数量的限制。 CXL 2.0 只允许这些处理设备中的一个出现在根端口的下游,而 CXL 3.0 则完全解除了这些限制。现在,CXL 根端口可以支持 Type-1/2/3 设备的完全混合匹配设置,具体取决于系统构建者的目标。值得注意的是,这意味着能够将多个加速连接到单个交换机,提高密度(每个主机更多的加速),并使新的点对点传输功能更加有用。

CXL 3.0 的另一大特性变化是支持多级切换。这建立在 CXL 2.0 的基础上,该版本引入了对 CXL 协议交换机的支持,但仅允许单个交换机驻留在主机及其设备之间。另一方面,多级交换允许多层交换机——也就是说,交换机馈入其他交换机——这极大地增加了所支持的网络拓扑的种类和复杂性。

即使只有两层交换机,这也足以实现非树状拓扑结构,例如环形、网状结构和其他结构设置。并且各个节点可以是主机或设备,对类型没有任何限制。

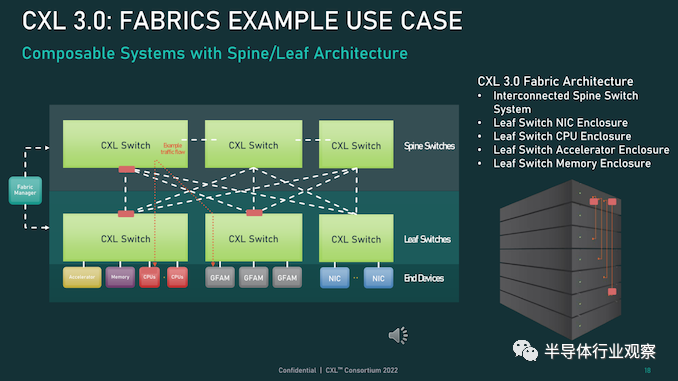

同时,对于真正奇特的设置,CXL 3.0 甚至可以支持主干/叶架构,其中流量通过顶级主干节点路由,其唯一工作是将流量进一步路由回包含实际主机的低级(叶)节点/设备。

最后,所有这些新的内存和拓扑/结构功能都可以在 CXL 联盟所称的全球结构附加内存 (GFAM) 中一起使用。简而言之,GFAM 通过进一步分解来自给定主机的内存,将 CXL 的内存扩展板(Type-3)理念提升到了一个新的水平。在这方面,GFAM 设备在功能上是它自己的共享内存池,主机和设备可以根据需要访问它。GFAM 设备可以同时包含易失性和非易失性存储器,例如 DRAM 和闪存。

反过来,GFAM 将使 CXL 能够有效地支持大型多节点设置。正如 ConsorTIum 在他们的一个示例中使用的那样,GFAM 允许 CXL 3.0 为在 CXL 连接的机器集群上实施 MapReduce 提供必要的性能和效率。当然,MapReduce 是一种非常流行的用于加速的算法,因此扩展 CXL 以更好地处理集群加速常见的工作负载是标准的下一步明显(并且可以说是必要的)。尽管它确实模糊了 CXL 等本地互连的结束位置和 InfiniBand 等网络互连的开始位置之间的界限。 最终,最大的区别可能是支持的节点数量。CXL 的寻址机制,联盟称之为基于端口的路由 (PBR),最多支持 2^ 12(4096) 个设备。因此,CXL 设置只能扩展至此,尤其是当加速、附加内存和其他设备迅速占用端口时。 总结一下,完整的 CXL 3.0 标准将于今天,即 FMS 2022 的第一天向公众发布。官方上,该联盟没有提供任何关于何时期望 CXL 3.0 出现在设备中的指导——这取决于设备制造商- 但有理由说它不会马上。随着 CXL 1.1 主机刚刚交付——更不用说 CXL 2.0 主机——CXL 的实际产品化比标准落后几年,这对于这些大型行业互连标准来说是典型的。

编辑:黄飞

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)