快速的开关速度、高阻断电压和较低的 R on用于电压转换器的高压 SiC MOSFET (》3 kV) 已经实现了新的应用,从而带来了诸如扩大开关频率水平、提高效率和降低损耗等优势。但是在设计电压传感器时要面临一些挑战,这些挑战与绝缘的严格要求以及与 10 kV SiC MOSFET 相关的更高 dv/dt (50-100 V/ns) 相关。有不同的方法可以测量中压电源的电压,其中一些是霍尔效应传感器、电容分压器、电阻分压器和电阻-电容梯。在理想条件下,我们可以在电阻分压器中找到无限带宽。

传感器设计

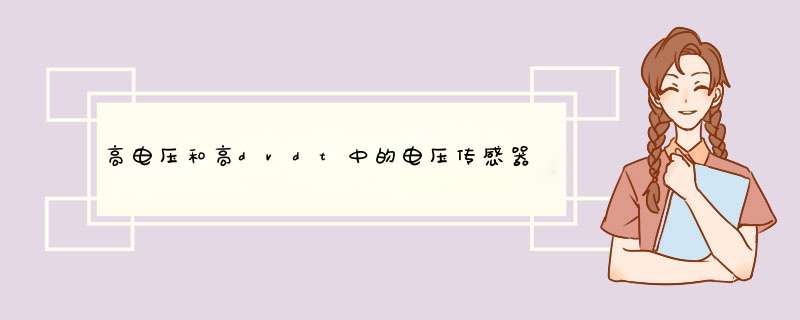

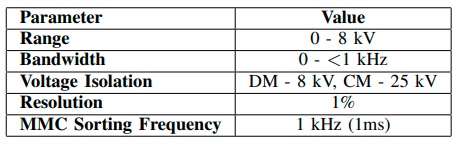

电源由两个隔离的栅极驱动器组成,每个驱动器为半桥,由 10 kV SiC MOSFET 组成,它们与 6.8 uF 子模块的电容组合形成 MMC 子模块。每个子模块的标称电压为 6.25 kV。表 1 总结了由转换器和 MMC 子模块确定的电压传感器设计要求。图 3 展示了一般的电压传感器设计。这种设计面临各种挑战,包括信号保真度、隔离设计和紧凑性。图 1 显示了电压传感器和测试装置的电路图。

表 1:电压传感器设计要求

图 1:测试装置的电路图

提高抗噪能力

通过检查和执行两个步骤来提高抗噪能力:噪声源和接地验证。

噪声源

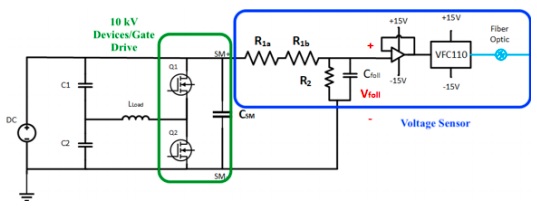

在 PEC 中观察到的一些主要噪声源是模数转换器、传感器和导致接地反d或 EMI 产生的高压 dv/dt 。对于来自电阻分压器的模拟信号的传输,选择了具有基于 sigma-delta 的电压到频率的转换器,以便它可以在光纤的帮助下将其传输数字化。MMC 相脚用于验证电压传感器的接地。图 2 显示了电压传感器的示意图。

图 2:电压传感器接地验证示意图

接地验证

在测试直流电压下,传感器连接到作为半桥子模块的高 dv/dt 点。类似的 dv/dt 将在最终的 MMC 中出现,并且子模块将暴露于其中。来自具有 0V 值的 VFC 的持续较高输出是必要的。

测试设置

使用较低电压设置来测试和调试电压传感器,这是通过将电阻分压器视为理想的并且存在于电路外来完成的。据观察,除非电压传感器在具有更高电压的环境中进行测试,否则不会出现关于噪声的问题。使用一个子模块作为半桥来测试电压传感器,并使用一个 175 mH 的电感器作为负载。为此目的选择了 10 kHz 的开关频率和 300 Hz 的基频。

结果

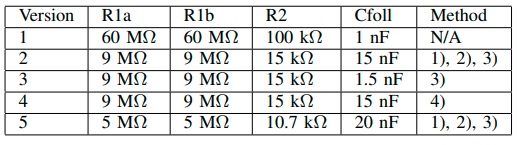

本节将重点介绍上面讨论过的所有改进和程序。表2描述了R 1 a、R 1 b、R 2和C foll 的值, 也显示在图1中。通过降低输入电压来提高 SNR 比来提高抗噪能力。这会导致功率损耗增加,但可以准确测量分压器。C的值也增加以减少带宽。这提高了抗噪性,但会导致延迟,因为增加的电容意味着增加的 RC 时间。布局和屏蔽也得到了改善,以确保信号完整性并减少传输线中的噪声耦合。

表 2:R1a、R1b、R2 和 Cfoll 的值

结论

本文分析了一些旨在改进噪声传感器的技术。电压传感器的主要误差来源是电阻分压器。其背后的原因是,在存在 IPC-2221 的情况下,这需要很大的绝缘距离,同时具有紧凑的设计以及具有 10kV 电压的 SiC 器件的高 dv/dt。为了提高电压传感器的噪声抗扰度,人们考虑了各种不同的点,例如:增加 SNR 以减少 BW,改变高压电阻串的布局,最后进行屏蔽。具有可复制能力且可靠的设计已用于测试噪声免疫传感器。所有数据均来自真实来源。

审核编辑:郭婷

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)