本文检查了 JFET SJEP120R100A 的功能和性能——这篇文章纯粹是指导性的;此组件不再可用。但是这种简单的方法也可以应用于其他新组件。在接下来的文章中,将使用其他组件——这种碳化硅 (SiC) JFET 可以成功地用于任何需要高功率和快速开关速度的应用。然而,它特别适合在音频行业中使用,它可以在高质量放大器中找到。

概述

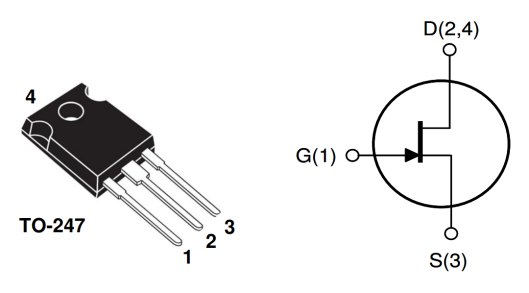

SJEP120R100A 是一种常关型 SiC 功率JFET(参见图 1)。它与所有标准集成电路兼容,即使在高达 150˚C 的温度下,它的切换速度也非常快,而且没有尾电流。它可以使用简单的方法与其他设备并联。让我们看一下它的一些基本特征,然后通过一些模拟来验证它们:

R DS(on) : 0.08 Ω (最大 0.1 Ω)

漏源阻断电压 (BV DSS ):1,200 V

连续漏极电流 (T J = 100˚C):17 A

连续漏极电流 (T J = 150˚C):11 A

脉冲漏极电流 (T C = 25˚C):30 A

短路耐受时间:50 µs

功耗(T C = 25˚C):114 W

栅源电压 (V GS ):–10 V 至 15 V

工作和储存温度:–55˚C 至 150˚C

图 1:JFET SJEP120R100A 及其引脚排列

要运行仿真,您必须首先在 Internet 上搜索组件的 SPICE 模型,然后可以直接在您选择的仿真器中使用该模型。或者,可以直接在设备上使用万用表和示波器进行测量。

.subckt SJEP120R100 DGS

.param R=530m ; R_gate

Rg G Gi {R} tc=-3m

Rd D Di 70m tc=8m 10u

Csd S Di 3p

Cgd G Di 43p

吉帝吉S SJEP120R100

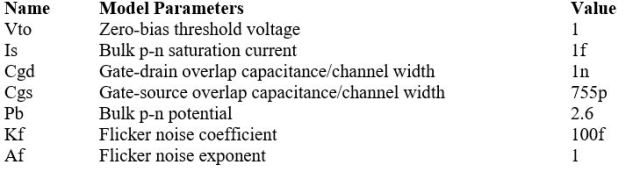

.model SJEP120R100 njf

+ Vto=1 贝塔=10.5 B=1

+ Lambda=2m Vk=2k 阿尔法=20u

+ 是=1f N=3.4

+ Isr=1n Nr=6.8

+ Cgd=1n Cgs=755p Pb=2.6 M=0.8

+ Kf=100f Af=1

+ VtoTC=-2m BetaTCe=-0.6 XTI=86

. 结束 SJEP120R100

该模型包含组件的主要电气和电子特性,例如:

导通电阻

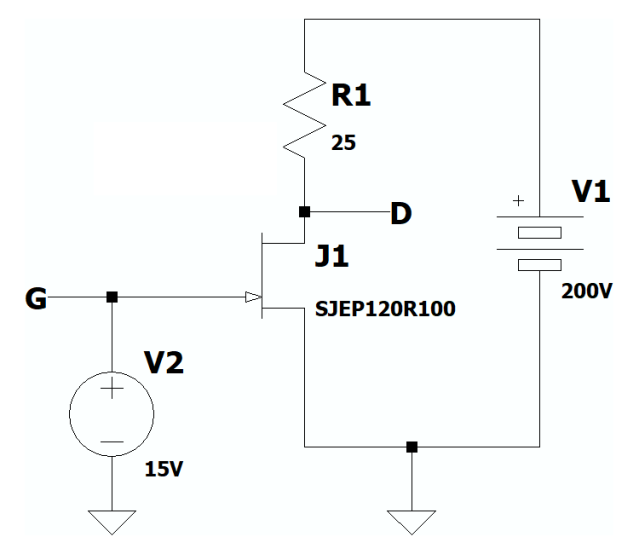

这可能是开发系统时要考虑的最重要的参数之一。在饱和状态下,它是组件为漏极和源极之间的电流流动提供的电阻。因此,R DS(on)是计算开关电源应用中传导损耗的重要指标。开关器件在关断时,其漏源电压异常高,但在导通时,电压下降到几百毫伏。因此,当这个数字尽可能低时,可以实现最佳效率,因为相对散热量下降。理想组件具有 R DS(on)等于 0,但目前,即使新技术大幅降低该值,也始终需要最小电阻。不过,应该注意的是,即使是最好的铜线或银线也不具有零电阻。为了获得通用结果,在计算 R DS(on)之前,必须在静态状态下测量漏极电流和漏源电压。图 2 显示了用于进行一些测量的器件饱和度的通用接线图。它由以下元素组成:

V1:200V主电源电压

V2:“栅极”驱动电压 15 V

J1:JFET SJEP120R100A

R1:25Ω 阻性负载

所有这些数字都是使用组件官方数据表中的“绝对最大额定值”数字计算得出的。当电路导通时,大电流从漏极流向源极,产生以下结果:

7.97 A 的漏极电流

807.7 mV 的漏源电压

器件功耗仅为 6.47 W

1,587-W 负载耗散(这是完全正常的)

在这种情况下,静态效率为 99.6%,这意味着所有电池电量都被负载有利地使用,而没有大量损失。

图 2:静态状态下的接线图

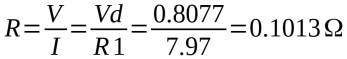

R DS(on)的计算公式如下:

这个结果完全符合官方数据表中的规格。

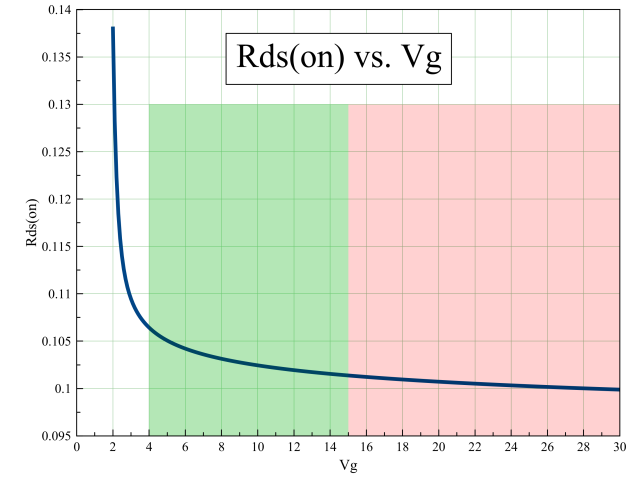

此值可能会因其他因素而显着变化。第一个依赖项指出,R DS(on) 随着栅极电压的增加而降低,同时明显在制造商的规格范围内。当栅极电压升得太高时,组件的可靠性会受到影响(参见图 3 中的图表)。

图 3:R DS(on)电阻与栅极电压的关系图

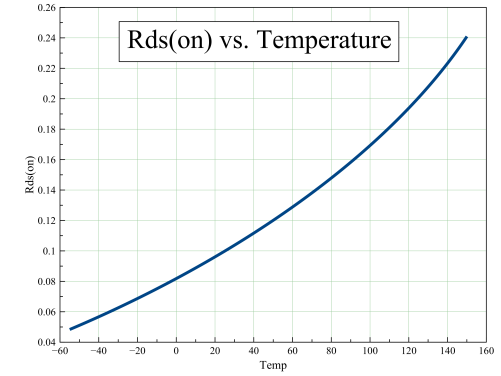

图 4:R DS(on)电阻与结温的函数关系图

在第二个相关性中,R DS(on)随结温而增加。高温是电子设计师的大敌,尤其是在大功率领域。出于这个原因,在组件过热的情况下,始终建议应用被动和主动散热器。如图 4 所示,R DS(on)值通常包括在相同的工作环境和施加在输出端的负载下的以下值:

–50˚C:0.0510536 Ω

–40˚C:0.056689 Ω

–30˚C:0.0625714 Ω

–20˚C:0.0687101 Ω

–10˚C:0.0751157 Ω

0℃:0.0818013Ω

10℃:0.0887818Ω

20℃:0.0960751Ω

30℃:0.103702Ω

40℃:0.111686Ω

50℃:0.120058Ω

60℃:0.128852Ω

70℃:0.13811Ω

80℃:0.147887Ω

90℃:0.15825Ω

100℃:0.169286Ω

110℃:0.181111Ω

120℃:0.193885Ω

130℃:0.207841Ω

140℃:0.223336Ω

150℃:0.240983Ω

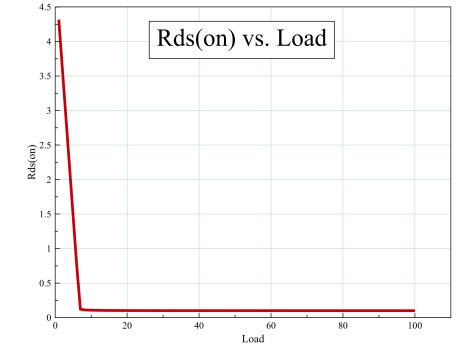

该图形完全符合制造商数据表的规格。第三个相关性,如图 5 所示,表明 R DS(on)对漏极上的电流不敏感,除非在极低负载水平下,器件在关键区域工作。

图 5:电阻 R DS(on)与施加到漏极的负载的关系图

SiC器件速度

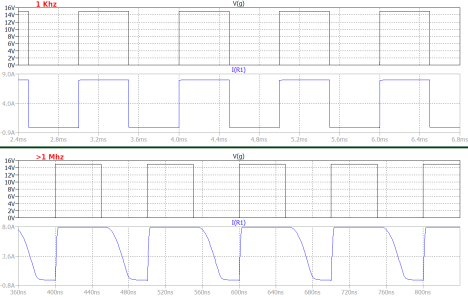

SiC 器件的真正性能最显着地体现在开关应用中,在这种应用中,它必须执行艰苦的工作才能以快速开关速率传输大量能量。SiC 器件与其直接前身有很大不同,特别是在高开关速度方面。因此,在为它们提供必要的激活电压和电流以及完全平滑的方形和矩形信号方面,它们必须先于高质量的驱动器。在低开关速率下(参见图 6 中的图表),这些组件显然不会引起任何问题,并且负载上的电流准确地跟随栅极上的驱动信号同相。

当运行速度继续增长时,负载上的电流不再能够完全跟随栅极上的信号,原因有多种,包括:

栅极电阻增加。

栅极的容抗上升到不可接受的水平。

开启延迟、上升时间、关闭延迟和下降时间参数越来越高。

因此,在高运行速度下,负载上存在的电流“拐点”在上升沿,最重要的是在下降沿变得明显。在这些情况下,当大量电压和电流值重叠时,开关损耗变得无法忍受,从而增加了作为无用热量浪费的功率。

图 6:SiC 器件的开关速度对组件性能有重大影响。

结论

所有上述测量表明,在使用 SiC 器件进行开关之前,设计人员应检查电力电子系统的 *** 作要求,并直接考虑制造商数据表上的组件规格。这是设计人员确保他们选择最佳设备的唯一方法。

审核编辑:汤梓红

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)