虽然硅基功率 MOSFET 在过去几十年中已经得到优化,但它们的电阻已经降低到了可能的极限。但是,对于碳化硅 MOSFET,还不能说同样的话。在其商业发布十年后,SiC 功率 MOSFET 制造商通常会随着每一代新器件的发布而将其特定导通电阻降低 30% 至 40%。正如本系列之前的文章(此处和此处)所讨论的,低导通电阻对于获得更小的芯片和器件至关重要,从而提高产量并最终提高利润。

本文基于PGC 咨询公司进行的分析,研究了当今的 650-V 和 1,200-V SiC MOSFET,揭示了这些问题,包括栅极氧化物可靠性的优化,这有助于降低比导通电阻,降低碳化硅成本。

在之前的文章中,我们看到了 Si MOSFET 多年来是如何不断改进的,以及它们如何仍然表现出出色的性能水平。然而,硅非常接近其技术极限,无法进一步降低特定导通电阻。结果,不能进一步增加可以从单个晶片获得的管芯数量。另一方面,SiC 提供了显着的改进空间,1,200 V 时的 R DS(on)比理论上可能的值高出 14 倍以上(650 V 时高出 33 倍以上),从而有机会实现更低的开关和传导损耗比等效额定的硅基 IGBT。

击穿电压注意事项

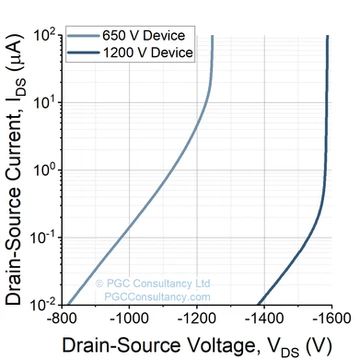

通过比较不同商用 MOSFET 的性能,PGC 咨询公司发现,具有最低特定导通电阻的同类最佳 650-V MOSFET 实际上在 1,250 V 时击穿。同样,同类最佳 1,200-V MOSFET 击穿电压降至 1,550 V,如图 1 的漏源电流与漏源电压曲线所示。这表明了 SiC 器件的过度设计程度。就上下文而言,最佳的硅器件将被设计为在略高于其额定电压的情况下击穿,并具有 50 至 100 V 的裕度。因此,最先进的商用 SiC 器件具有远高于该电压等级严格要求的漂移区电阻。

图 1:测得的 650V 和 1,200V 额定 SiC MOSFET 的击穿电压

解释 SiC MOSFET 过额定的主要原因是栅极氧化物的可靠性。虽然 SiC 能够承受高临界电场,但栅极氧化物泄漏(及其可靠性)与穿过它的电场成正比。例如,如果一个 650V 的器件在 700V 时真正击穿,则栅极下方的高电场会导致良率问题,并且在栅极应力老化鉴定期间,很大比例的器件会出现故障。因此,漂移区的过度设计以承受更大的电压,实际上是降低了 MOSFET 的额定值,以确保栅极可靠性。

SiC MOSFET的分压电阻

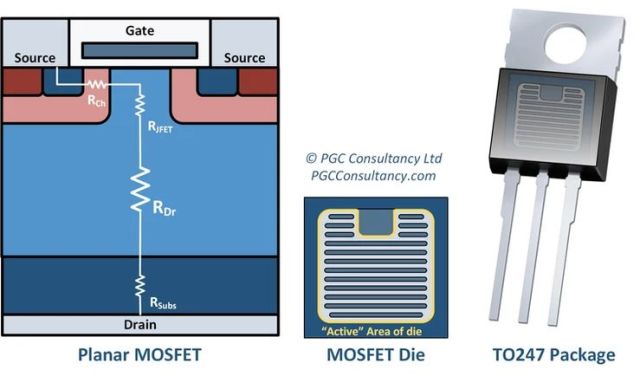

如图 2 所示,SiC MOSFET 的电阻由不同因素组合而成。其中,唯一与阻断电压成函数关系的分量是漂移区电阻 (R Dr )。所有其他固定电阻元件应小于 R Dr,从而使器件能够像 Si 器件一样处于理想的单极极限。

图 2:影响 SiC MOSFET 电阻的因素

最大的固定电阻包括高掺杂衬底 (R Subs )、沟道电阻 (R Ch ) 和来自 JFET 区域的电阻 (R JFET )。此外,总电阻仅考虑器件的有源区域,因此不考虑器件周边的 SiC 区域,这些区域属于终端和划线通道,即不打算承载任何电流的区域。

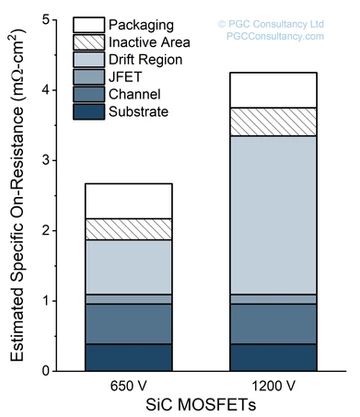

图 3:PGC 咨询模型

图 3 显示了 PGC 咨询公司如何模拟每个组件在确定 650 V 和 1,200 V 额定器件的整体 SiC 特定导通电阻方面的影响。两种器件之间的主要区别在于漂移区,而其他组件的贡献实际上与电压无关。

在固定贡献者中,通道阻力最大。氧化时,硅和 SiC 都会产生二氧化硅 (SiO 2 ),它是 MOS 晶体管中使用的绝缘体。在硅的情况下,这个过程会产生一个几乎完美且光滑的界面,不会阻碍电子通过它。然而,当 SiC 被氧化时,它的一些碳仍然被困在 SiO 2 /SiC 界面中,当电子从其下方通过时,这会散射电子。因此,SiC 的沟道迁移率约为 20 至 30 cm 2 /Vs(与硅的 200 cm 2 /Vs 相比),因此,SiC 的每单位长度的沟道电阻是 Si 的 10 倍。

衬底电阻来自SiC的N+起始衬底,具有较高的电阻率。这种电阻通过减薄来降低,大多数芯片制造商正在将制造后 350-µm SiC 衬底的厚度降低到 100–150 µm 的事实证明了这一点。

在平面设计中,可以通过在栅极下方使用更高掺杂的区域(称为“电荷存储层”)来降低 JFET 区域的电阻。在沟槽设计中,该组件的贡献被消除了。

碳化硅限制

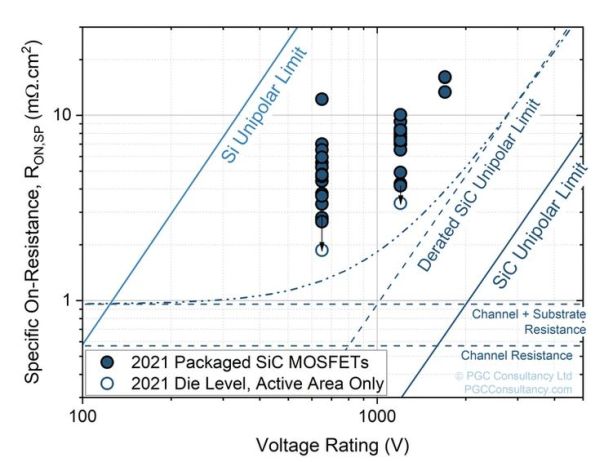

可以更新上一篇文章中介绍的 SiC 的单极极限图,添加空心圆圈,这是在减去估计的封装电阻后重新计算的同类最佳 MOSFET,并且仅使用模具(见图4)。

图 4:增加电阻后修改的单极极限图

图 4 中还添加了 SiC 通道和衬底电阻的估计值,表示为与电压无关的水平线。“降额 SiC 单极极限”曲线表示必须将 MOSFET 降额至其潜在电压额定值的 50% 以确保栅极氧化物可靠性的效果。最后,点划线是固定电阻和降额漂移区的添加,显示了最先进的 SiC 技术。

解决栅极氧化物问题是所有 SiC 芯片制造商的首要任务,因为它有助于降低通道电阻和降额。同时,更薄、电阻更低的基板将有助于进一步降低损耗。

审核编辑:彭静欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)