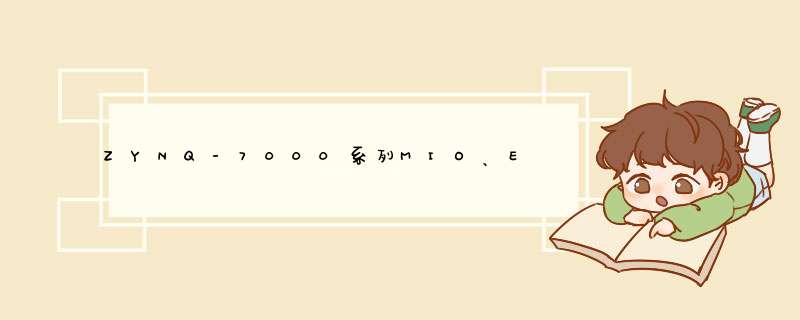

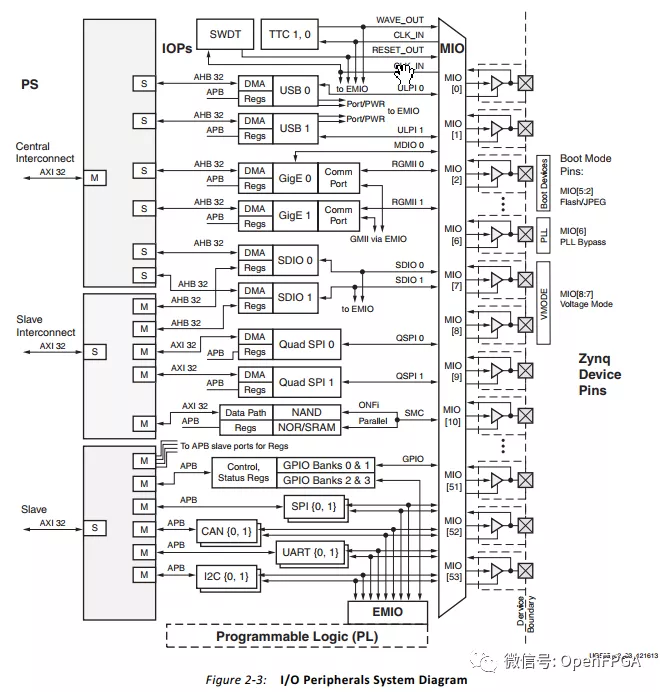

PS部分框图如上图所示,PS 和外部接口之间的通信主要是通过复用的输入 / 输出( MulTIplexed Input/Output,MIO)实现的,它提供了可以做灵活配置的 54 个引脚,这表明外部设备和引脚之间的映射是可以按需定义的。这样的连接也可以通过扩展 MIO (ExtendedMIO,EMIO)来实现,EMIO 并不是 PS 和外部连接之间的直接通路,而是通过共用了PL 的 I/O 资源来实现的 。这些都出现在上图的左侧。当需要扩展超过 54 个引脚的时候可以用 EMIO,而当 PL 中实现了一个 IP 包的时候,这也是 PS 和 PL 中的IP 包接口的一种方法。

可用的 I/O 包括标准通信接口和通用输入 / 输出 (General Purpose Input/Output,GPIO),GPIO 可以用做各种用途,包括简单的按钮、开关和 LED。

在ZYNQ7000系列PS中除了上面提到的MIO和EMIO之外,还包括AXI_GPIO。

这三者关系如下:

其中MIO和EMIO是直接挂在PS上的GPIO。而AXI_GPIO是通过AXI总线挂在PS上的GPIO上。

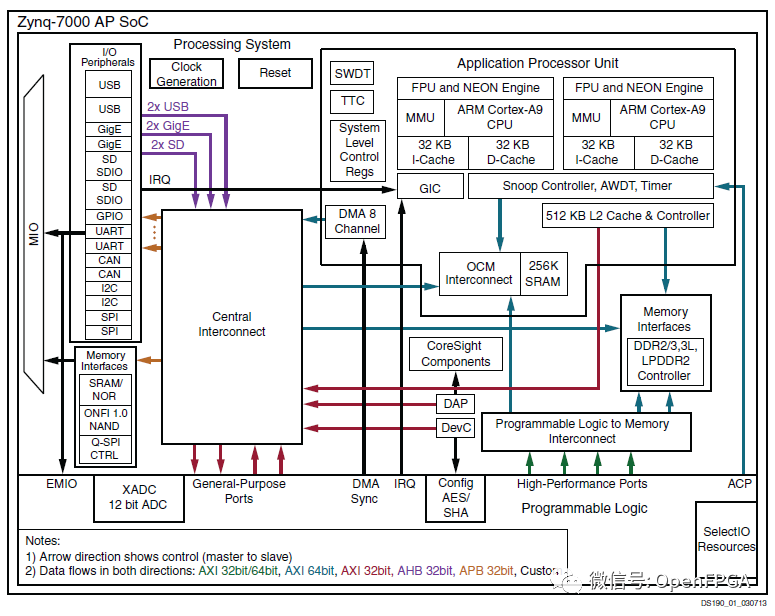

我们先看一下MIO和EMIO:下图EMIO和MIO的结构。其中MIO分布在BANK0,BANK1,而EMIO则分布在BANK2、BANK3。

注意一下几项:

首先、MIO在zynq上的管脚是固定的,而EMIO,是通过PL部分扩展的,所以使用EMIO时候需要在约束文件中分配管脚,所以设计EMIO的程序时,需要生成PL部分的bit文件,烧写到FPGA中。

其次、由下图可以看出MIO共占54bit,而EMIO占64bit。其中MIO占用IO号为0-53。而EMIO占用IO号为54-117。

再者、无论是EMIO还是MIO都属于PS上的IO,直接由PS *** 作。在调用头文件,只调用#include "xgpiops.h"即可,而在调用AXI_GPIO时,则需要#include "xgpio.h"。

关于EMIO:

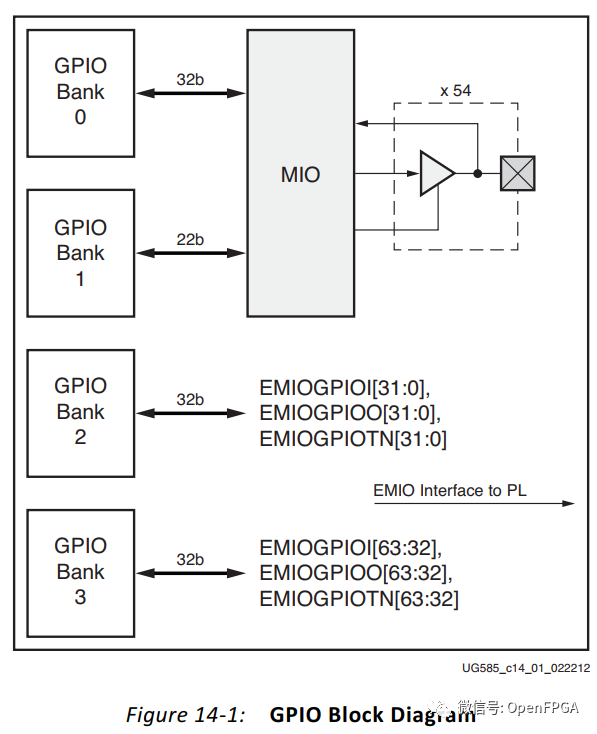

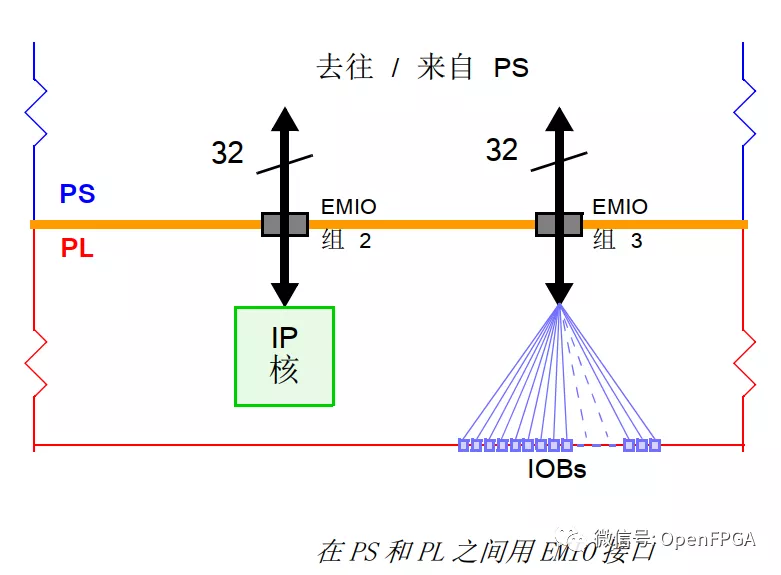

从 PS 出来,有几种连接可以经由 PL 到外部接口上,这被称作扩展的 MIO (Extended MIO) ,即 EMIO。

EMIO 涉及到两个域之间的信号传输,是由一组简单的导线连接实现的,因此,EMIO 并不支持所有的 MIO 接口,而支持的那些中,也有些的能力受到了限制 。这些连接被安排成两个 32 位的组。

很多情况下,经由 EMIO 的接口是直接连接到所需的 PL 的外部引脚上的,这个连接是由一个约束(描述)文件中的条目所指定的。在这个模式下,EMIO 可以实现额外的 64 个输入线和 64 个带有输出始能的输出线。另一个选择是用 EMIO 来连接PS 和 PL 里的外设模块。下图描绘了这两种使用模式 :

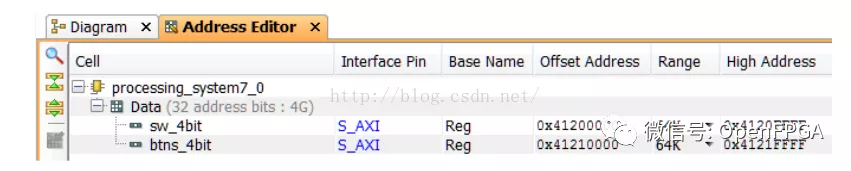

最后看一下,AXI_GPIO相当于GPIO的IP核,我们调用时是占用相应AXI总线地址空间,如下图,占用地址为0x41200000和0x41210000

审核编辑 黄昊宇

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)