降低功耗是现代芯片设计最具挑战性需求之一。采用单点工具流程时,往往只有到了设计流程后期阶段才会去考虑降低功耗的需求,从而经常导致大量问题和延时。微捷码设计自动化有限公司高级技术产品经理Rob Knoth向我们解释了‘为何功率优化应是完整设计流程必不可少的集成组件’。

起初,低功耗设计技术主要是用于移动产品。而今插在电源插座上的产品数不胜数,它们都在不断吸收着电流,全世界大量功率都浪费在了这些产品上。今天,政府正积极要求电子企业遵从更严格的要求来帮助降低全球功耗。低功耗设计与每个人息息相关。现在低功耗需求无处不在,而且变得更具挑战性。

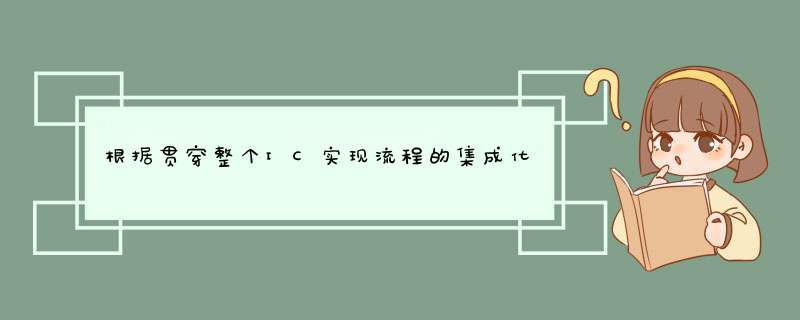

低功耗设计,不论是动态功耗还是静态功耗,均要求设计流程各个阶段时序、功耗和面积间复杂的折衷权衡。这些需求相互间联系密切,要想解决这些需求,低功耗分析和优化引擎必须集成并运用于从RTL规格到GDSII输出的整个流程中。由于芯片尺寸还在持续增长,因此这一流程必须是可缩放的,否则它将会对设计师工作效率造成限制。

图1: 低功耗设计牵涉到设计流程的各个方面

动态功耗

设计的动态功耗是由电容、电压和频率共同决定的。

电容主要受到门极电路尺寸及布线的影响。逻辑门尺寸是降低内部开关电流与增加系统面积、噪音和容性负载间的一种折衷权衡。缩短布线将意味着容性负载的减少,但是带来拥塞情况的恶化,可能导致布线违规或源自串扰的时序问题。

频率对系统动态功耗的影响很大。采用并行处理方式,系统时钟可以降低,同时保持吞吐量不变。当然这是以牺牲面积为代价,是从架构上进行考虑。

在芯片总功耗中,时钟树网络的功耗占据了很大一部分。将功耗作为一个成本函数来考虑已变得越来越重要,特别在较小尺寸中更是如此。目前已有各种不同技术可被广泛应用于RTL综合和物理综合中,如:广泛的门控时钟覆盖、门控时钟克隆/反克隆、有功率意识的缓冲器插入、尺寸调整和门控时钟布局。此外,如时钟树综合(CTS)中多阈值电压(MulTI-Vt)、层次化时钟门控、基于行为的时钟门控等其他技术也可以提供额外的功率节省。门控技术降低动态功耗也必须在面积和静态功耗上平衡折中。

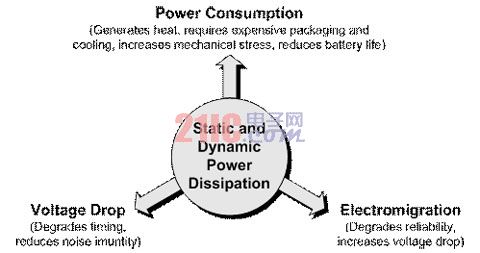

其中一项标准技术是将设计分为大量“电压岛”(图2)。虽然供电电压较低的电压岛,其性能也就较差,但其动态功耗也将大幅降低。

图2. 多电压域(mulTI-Vdd)设计类型。

在将设计分为多个电压岛时,信号从一个电压域到另一个电压域传输必须要插入适当的电压转换器或隔离元件。一个真正有功耗意识的设计环境应该能够自动插入这些单元并做好其验证工作。

由电压岛和降频技术所组成的动态电压和频率缩放(DVFS)是最先进的一种降低动态功耗方式。系统可被设计为各个功能块按照不同的电压和频率组合工作,随着器件的 *** 作模式变化而变化。这就是为什么多核处理器能具有长待机的电池寿命和高效的按需计算能力的原因。

静态功耗

在当今的工艺技术中,不工作时元器件的漏电流是个大问题。这种电流与温度和开关阈值成指数关系,给功耗优化工作带来了很大困难。

解决静态漏电问题的一种方式采用具备多阈值电压(Vt)元器件的库,在设计中一部分使用低阈值晶体管,其它部分则使用高阈值晶体管,不过这只能解决部分问题。其中低阈值晶体管开关速度较快但漏电流较高、功耗较大;而高阈值晶体则开关速度较慢但漏电流较低、功耗较小。

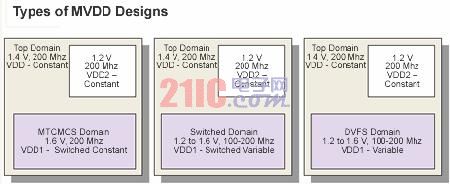

还有一种方式是利用高阈值电压(high-Vt)开关来有选择地切断设计中未工作部分的电源。利用高阈值电压开关来连接全局恒定电源线轨与局部开关电源线轨,让局部线轨的电源根据需要开启或关闭,这就提供了对功率门控的细粒度、中粒度和粗粒度的控制能力(如图3)。

图3. 多阈值CMOS晶体管能被用于功率门控,通过提供对局部电源导轨的细粒度控制从而降低功耗。

不过,所有这些方式都必须与功率分布网络设计工作同步进行,而不是在设计流程后期单独进行。首先,早期线轨分析必须在电源网格还未完成时执行,这样耗能元件才可均匀地分布在芯片中,避免热点和局部电压降问题。其次,要有选择地使用线宽算法来解决电压降和电迁移问题。当然,这些技术都要求有早期集成化分析。

设计工具

传统上,单点的功耗分析和优化工具被作为单独步骤添加到流程中。这些流程要么需要采用多个数据库,要么是将完全不同的数据模型组合进一个数据库中,不仅带来了数据转换问题,同时也使得数据管理工作变得相当烦琐、耗时且容易出错。

不止如此,更严重的问题还在于,单点工具在布局后修正缺陷的做法极难完成,特别是修正工作还必须手工进行时更是如此。且分析和修正工作必须不断重复进行,可能导致代价昂贵的项目延迟。如果分析工作是设计流程的其中一个组成部分,那么就能更早地发现问题,给出解决方案,也就能避免了修正工作。

为什么一款基于单一数据模型的集成化流程是必需的呢?DVFS设计就是一个很好例子。为确保系统在缩放时仍可正常运作,我们需要一种适用于多 *** 作模式和环境的分析和优化的稳定集成。随着当今片上系统(SoC)尺寸达到了1亿个门极电路,这种分析和优化还必须有效的使用存储器和降低运行时间。当前行业标准的静态时序工具是在多模/多角分析日渐普遍使用前开发出来的。现在它们的效率越来越低,而且还需额外且昂贵的硬件和资源。为支持1亿门、低功耗系统的生产率需求,创新工作势在必行。

未来

低功耗设计需求随着其重要性的日益突显,正成为一项研究热点。

通过工艺技术的变化,静态功耗问题得到了一些解决。例如,人们正在开发可提供近零漏电流和更先进细粒度功率门控技术的高k(高介电常数)和金属栅半导体。

通过异步设计降低动态功耗的研究还在持续进行,可能不久我们就能看到回报了。其主要优势是去除了恒定开关同步时钟网络,从功率、面积和时序角度来看,这能带来很好效果。遗憾的是,高效并且健壮的自定时逻辑电路的自动生成仍未实现商业化。 目前应用仅仅局限于隔离的功能块(GALS),外围使用异步的方式,而内部依然使用同步电路。

总结

只有功耗分析工具全都与实现工具并行运行才是真正的低功耗实现环境,其中必须包括综合、布局布线、时钟树综合、提取、时序和信号完整性分析,且它们全都使用统一数据模型,可以同时访问分析结果。解决方案必须具有可缩放性,能应对有着更严格功率要求的更大型设计,这点至关重要。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)