英特尔公司最近宣布他们将退出嵌入式市场。在1970年代,英特尔通过引入8048 μC创造了嵌入式市场,随后8051μC的普及应用极端火爆。但是,该公司将停止生产8051、251、8096/196、188/186、i960、所有版本的386 (包括386EX)和486,总计起来,大约700种器件型号正在停产。采用基于ASIC的μC/μP (微控制器/微处理器)的客户预期,其它的供应商也将做出器件过时的宣告,特别是那些最近被私人股权投资公司收购的、要减产特定的μC/μP的供应商,他们可能导致所提供的产品被合并。

大多数设计工程师都关注器件的过时问题,在工业、科学、汽车和医疗市场的工程师对此问题更为关注。因为这些市场的产品生命周期长,基于ASIC的μC/μP可能是开发一个产品的成本极高的方法;因为假如μC/μP停产,那么,它就可能涉及对PCB、软件接口、板级支持封装(BSP)开发、验证、测试和对整个最终产品进行多次质量认证的再一次工程努力。

大多ASIC供应商确实提供诸如最后一次购买(LTB)和硅晶圆购买计划之类的替代解决方案,但是,两种选择的成本都是高昂的。很难预测(更合适的说法是“猜测”)在产品生命周期中需要采购和存储多少μC/μP,与此同时,库存管理正试图避免在货架上把巨大数量的元器件存放几个月或几年。

软性、灵活的“生命终止”解决方案

当与软处理IP核相结合时,可编程嵌入式平台提供独一无二的优势。采用一种软处理IP核及几个现成的FPGA系列,你可以利用嵌入式行业中范围广阔的不同应用的优势以及跟分立器件市场相关的不确定性。

回避退化风险的一种最佳解决方案是利用在硅器件层上的灵活FPGA构造及具有定制外设的软IP处理器。赛灵思为英特尔以及其它供应商的生命终止器件提供多种解决方案。

这些解决方案依赖于你现有的软件代码基础。如果它是采用汇编语言编写的,一种选择是把代码与C语言对接;如果这种办法不可行,你可以试用Xilinx® AllianceCORE™合作伙伴网络提供的像186和8051一样成熟的μC/μP IP模块。这将包括把外设集成到你特定的生命终止器件型号并进行验证和测试。

图1:设计选项。

Intel 188/186 Features 英特尔188/186功能

MicroBlaze with Memory Controller 具有存储控制器的MicroBlaze

CPU StaTIc No Cache (12, 20, 25 MHz) CPU静态没有高速缓冲存储器

MicroBlaze CPU Core with 16K Cache (104 MHz) 具有16K高速缓冲存储器的MicroBlaze CPU核

Clock Generator 时钟发生器

DCM on Xilinx FPGA 在Xilinx FPGA上的DCM

用于外部存储器和I/O的独立DMA通道

OPB Central DMA Controller OPB中央DMA控制器

Three Programmable 16-Bit TImers 三可编程16位定时器

OPB TImer/Counter (Four)材OPB定时/计数器

Local Bus Controller 本地总线控制器

OPB Bus Interface OPB总线接口

DRAM Refresh Control Unit DRAM刷新控制单元

OPB Memory Controller Interface OPB存储控制器接口

Programmable Interrupt Controller 可编程中断控制器OPB Interrupt Controller OPB中断控制器

Programmable Wait State Generator 可编程等待状态发生器

State Machine or an OPB TImer/Counter (Included Above) 状态机或OPB定时器/计数器(包括上面)

Chip Select Logic 片选逻辑

OPB GPIO片上外设总线 (OPB) 通用IO (GPIO)

System-Level Testing Support 系统级测试支持

OPB JTAG UART

如果现有的软件代码采用C语言编写,赛灵思已经在Spartan™、Virtex™ FPGAs、PowerPC™ μP 32位 RISC嵌入式Virtex FPGA系列以及流行的MicroBlaze™ 软IP处理器中提供了真正的不会过时的解决方案。

MicroBlaze软处理器是一种具有5级管道执行以减少每条指令占用的时钟数(CPI)的32位RISC处理器。该产品的供货已经有5年时间,最新的版本是MicroBlaze v5.0,它是100%二进制向下兼容的。二进制向下兼容性意味着可以运行较老的MicroBlaze版本或不需要软件对接就能在MicroBlaze v5.0系统上运行以前的代码。这就确保了基于MicroBlaze的μC设计真正不会过时。随着未来版本的MicroBlaze软IP处理器的推出,用户将不需要考虑任何过时问题就能够从较新的功能集上获益。

当对性能进行了配置之后,MicroBlaze v5.0处理器以210 MHz的速度运行在Virtex-5 LX器件上。赛灵思在嵌入式开发工具套件(EDK)包中向客户免费提供MicroBlaze软处理器许可证,此外,不存在单位版税,所以,不论你销售的是一片或是一百万片芯片,你都可以拥有你自己特定的MicroBlaze设计。

为了使你能够开发一种针对你自己应用的特殊、灵活和独一无二的解决方案,赛灵思已经开发了称为Platform Studio的集成开发环境(IDE)。Xilinx Platform Studio (XPS) IDE和工具套件被包含在EDK包之中。XPS 提供让你在系统的软件和硬件层中定制各种解决方案的真正灵活的工具。XPS的组成部分包括:一套称为基本系统构建器的快速IP生成工具(BSB);一套基于GNU/GCC的软件开发工具;一套称为XMD的处理器除错引擎;一套称为SDK的基于Eclipse的软件开发套件;一套处理IP外设模块的扩展库;MicroBlaze 32位RISC处理器。

赛灵思嵌入式处理器获得了由RTOS(实时 *** 作系统)中间件、除错和电子系统级(ESL)工具供应商组成的生态系统的支持,他们也将有助于你定制自己的产品。

平台IP

赛灵思利用MicroBlaze处理器、外设、SDRAM和闪存控制器提供一种等效于“生命终止”器件的设计。这种来自英特尔公司和其它供应商的针对“生命终止”器件的预集成参考设计解决方案被称为Platform IP,这种解决方案使你能够快速地开发并部署真正不过时的方案。

例如,对于英特尔公司的186/188XL系列,表1列出了在这些产品上的外设和它们的赛灵思等效IP模块。

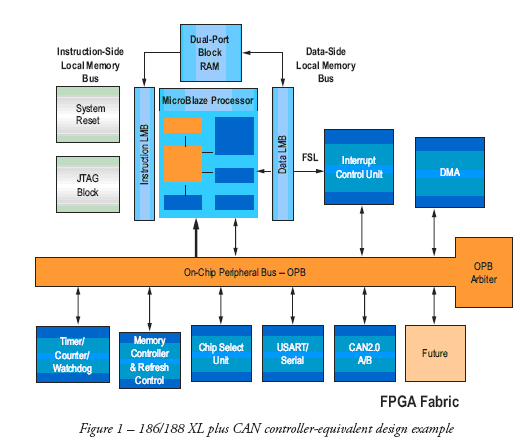

图1:186/188XL加上等效于CAN控制器的设计例子,该方案的组成部分包括:

•一个Spartan-3E FPGA平台;

•一个以104 MHz速度运行在Spartan-3器件上的MicroBlaze 32位RISC CPU;

•等效于186/188XL的通用外设;

•内部存储器SDRAM和闪存控制器;

• CAN (控制器区域网络)2.0 A/B MAC

这种灵活的系统设计可以减少各种风险,因为你可以把任何将来的要求以新的定制逻辑模块、DSP、外设或第三方IP的形式添加到FPGA之中。 此外,该系统还可以被方便地重新配置。

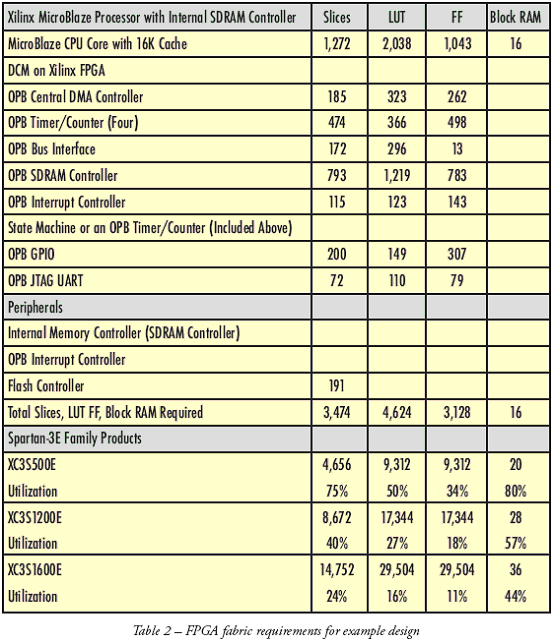

在表2中的设计表示的是对FPGA构造的有效使用。赛灵思的Platform IP以参考设计的形式为英特尔公司和无数其它供应商的“生命终止”产品提供解决方案,使你能够快速地部署针对你的过时器件的解决方案。

图1:186/188XL加上等效于CAN控制器的设计例子

Instruction-Side Local Memory Bus 指令侧本地存储器总线

Dual-Port Block RAM 双口模块RAMData-Side Local Memory Bus 数据侧本地存储器总线

System Reset 系统复位

JTAG Block JTAG模块

MicroBlaze Processor MicroBlaze处理器

Instruction LMB 指令LMB

Data LMB 数据LMB

FSL快速单工连接

Interrupt Control Unit 中断控制单元

DMA 直接存储器存取

On-Chip Peripheral Bus –片上外设总线 (OPB)

OPB Arbiter OPB仲裁器

Timer/Counter/Watchdog 定时器/计数器/看门狗

Memory Controller & Refresh Control 存储控制器和刷新控制

Chip Select Unit 芯片选择单元

USART/Serial USART/串行口

CAN2.0 A/B

Future 将来的需求

FPGA Fabric FPGA构造

表2:针对实例设计的FPGA构造要求。

=====================

Xilinx MicroBlaze Processor with Internal SDRAM Controller

具有内部SDRAM控制器的赛灵思MicroBlaze处理器

Slices 逻辑片

LUT 查找表

FF触发器

Block 模块

RAM随机存取存储器

MicroBlaze CPU Core with 16K Cache 具有16K高速缓冲存储器的MicroBlaze CPU核

DCM on Xilinx FPGA 在Xilinx FPGA上的DCM

OPB Central DMA Controller OPB中央DMA控制器

OPB Timer/Counter (Four) OPB定时器/计数器

OPB Bus Interface OPB总线接口

OPB SDRAM Controller OPBSDRAM控制器

OPB Interrupt Controller OPB中断控制器

State Machine or an OPB Timer/Counter (Included Above) 状态机或一个OPB定时器/计数器(包括上面的)

OPB GPIO片上外设总线 (OPB) 通用IO (GPIO)

OPB JTAG UART

Peripherals 外设

Internal Memory Controller (SDRAM Controller) 内部存储控制器(SDRAM控制器)

OPB Interrupt Controller OPB中断控制器

Flash Controller 闪存控制器

Total Slices, LUT FF, Block RAM Required 总的逻辑片,LUT FF,所需要的模块RAM

Spartan-3E Family Products Spartan-3E系列产品

XC3S500E

Utilization 利用率

XC3S1200E

Utilization 利用率

XC3S1600E

Utilization 利用率

=========================

结论

所有的芯片制造商都将在某一个时间点对某些产品实施停产,但是,FPGA是可编程、可再编程且可现场升级的。因此,作为一个FPGA用户,当你为利用成本、密度和功耗趋势而在FPGA平台系列上进行代码移植时,你可以确信你花费多人年所做的软件开发可以被安全地投资到一个嵌入式目标设计之中,该嵌入式目标设计可以继续运行同你第一天编制的代码一样的软件代码,即使它可能正在新的硬件上运行。

赛灵思处理核使客户能够有效地利用FPGA构造并有效地管理成本。当MicroBlaze和PicoBlaze 处理器(后者是采用汇编语言编写的8位参考设计)被嵌入到FPGA构造之中时,通过你现有和配置的稳定的平台,可以消除处理器过时的问题。随着Spartan系列到Virtex 系列FPGA的应用范围向商用和汽车级工业领域的跨越,软处理器成为防止设计过时的理想解决方案。你不仅仅能够获得可编程逻辑所提供的灵活性、一体化和可升级性,而且可以获得专门满足你的设计要求而定制的处理器。

MicroBlaze处理器的软件本质意味着它可以被例示到无数的平台FPGA器件之中,覆盖广泛的器件配置和价格点。完全采用软处理器核和可定制IP就可以替代你的过时器件。因为MicroBlaze解决方案是软处理器IP核,你的设计永远不会因一个处理器芯片的“生命终止”而过时,后续版本将保持100%的二进制向下兼容性。此外,源代码许可协议是现成的。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)