分布式系统需求

您通常可以将大型系统分解为多个不同组件,独立实现每个组件的硬件和软件。要提供更高计算能力和I/O容量,您可以在不同硬件上实现系统的各个组件。

例如,飞机的襟翼、缝翼、方向舵、引擎、副翼等都需要仿真和测试。可以如图1所示,将系统分解为多个硬件部件,从而使用模块化方法。

图1. 可以用多个PXI系统仿真飞机组件

系统级集成特性

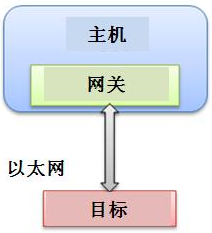

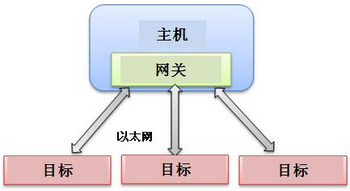

使用NI VeriStand 2010,一个或多个 *** 作者(主机)计算机可以在最少用户配置的情况下,与一个或多个实时执行目标进行通信。NI VeriStand处理 *** 作者计算机(主机)与实时执行目标之间的通信。图2给出了包含主机和目标的简单拓扑结构。

图2. 简单拓扑结构

主机用于和目标通信的组件是NI VeriStand Gateway。虽然通信管理是自动完成的,它是理解大型拓扑结构所需的重要概念。

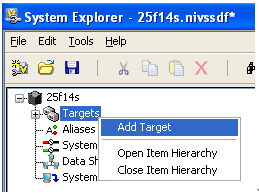

您可以方便地在NI VeriStand 2010系统浏览器中将目标添加到拓扑结构中。

图3. 在系统浏览器中添加目标

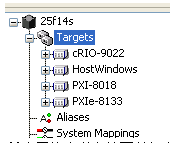

单个系统定义文件可以包含无限多个目标,甚至可以混和不同目标类型。

图4. 单个系统定义文件可以包含多个目标

每个目标有自己的专用硬件和软件配置,所有目标可以通过单个网关实现部署和交互。

图5. 可在单个主机上部署多个目标并进行交互

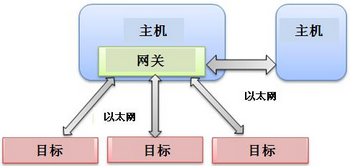

通过与另一个主机网关进行通信,其他主机计算机可以与相同的拓扑结构进行通信。

图6. 多个主机与多个目标拓扑结构

要完成这点,其他主机只需要修改NI VeriStand网关地址为远程主机即可。其他应用程序保持不变。

在分布式计算机之间共享数据

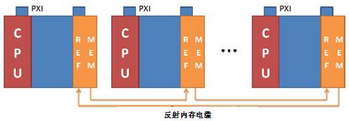

要让分布式系统如同单个系统一样工作,必须在系统组件之间共享数据。这是让不同部分可以一起工作的关键要素。通常可以使用反射内存接口实现。

反射内存网络是实时本地局域网(LAN),每个计算机总是拥有共享内存集合的最新本地复本。这些专用网络是为了提供高确定性的数据通信而专门设计的。可以提供多种分布式仿真和工业控制应用所需的高级定时性能。反射内存网络获益于通用数据网络,是不同需求推动下产生的完全独立的技术,适用于要求确定性、简单实现和软件负荷小的应用程序1。

反射内存为NI VeriStand提供了在多个目标之间共享数据的能力,并且满足了整个系统的性能与确定性需求。使用反射内存,仿真模型可以分割在不同的目标系统上同时执行。输入与输出数值通过反射内存在不同目标系统上共享。GE Fanuc反射内存板卡本地支持NI VeriStand 2010。NI VeriStand 2010的许多组件可以使用反射内存无缝创建多目标系统。

此外,NI VeriStand 2010将数据在目标之间自动分步用于不同的用途。例如,您可以配置激励(测试)档案运行在需要目标B数据的目标A上。NI VeriStand 2010在目标之间自动创建并激活链路获取数据。这可以在无需用户配置的情况下自动完成。

图7显示了包含反射内存板卡的实例系统。

图7. 使用反射内存的多个机箱

同步分布式系统

在设计系统时,考虑时序与同步的需求是十分重要的。如果分布式硬件不进行同步,输入和输出的采样将不同时发生。另外,随着时间的推移,漂移会导致系统的一个组件比另一个组件得到更多采样,尽管它们被配置为同样的速率。如果仿真是您的目标,这将导致问题。例如,两个襟翼仿真可能处于不同的时间状态。另外,因为数据并非来自相同的时间点,数据记录和分析将被破坏。

同步基础概要介绍了例如时钟漂移和时钟偏差的许多细节。

分布式系统的同步包括硬件同步和软件同步。您可以选择性地将整个系统与GPS或IRIG等外部时间参考进行同步。

硬件同步

硬件同步意味着系统的每个硬件共享一个硬件参考时钟,用于定时和开始I/O任务。系统中的每个硬件都利用相同的硬件参考时钟生成其自己的时钟,每个硬件都在相同的时间开始。

常见的硬件定时和同步任务实例包含多个数据采集板卡的同步采样,在更新数据采集模拟输出同时,更新现场可编程门阵列(FPGA)板卡数字输出PWM的占空比,在数字万用表(DMM)与开关之间握手,波形发生器和数字化仪的锁相,或者射频(RF)下变频器和中频(IF)数字化仪的同步。

您可以用NI PXI机箱创建NI VeriStand分布式系统。PXI(PCI eXtensions for InstrumentaTIon,面向仪器系统的PCI扩展)是基于PC的坚固平台,提供了用于测量与自动化系统的高性能低成本部署解决方案。PXI将外设组件互连标准(PCI)电子总线与坚固的CompactPCI模块化Eurocard机械封装结合在一起,并增加了专用同步总线和关键软件特性。

机箱包含高性能PXI背板,其中包含PCI总线和定时与触发总线。PXI模块化仪器增加了10 MHz专用系统参考时钟、PXI触发总线、星型触发总线和槽对槽局部总线,满足了高级定时、同步与边带通信的需求,并且不损失任何PCI的优点。

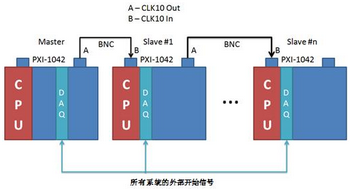

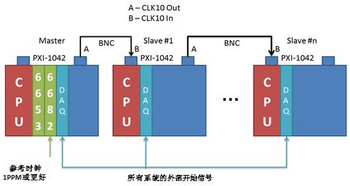

在PXI机箱之间共享参考时钟最简单的方法是使用机箱背部的CLK10 BNC接头。几乎所有的现代PXI机箱都有BNC端子。每个机箱有CLK10输出接头和CLK10输入接头。将机箱的CLK10输出与另一个机箱的CLK10输入相连,就可以确保使用相同的参考时钟。

要共享开始触发器,推荐使用NI数据采集(DAQ)设备。一个机箱可以将触发信号导出供一个或多个其他机箱作为开始信号使用。

图8 是硬件同步配置的例子。在这个配置中,NI PXI-1042主机箱利用BNC电缆将CLK10作为时钟参考导出到N个其他PXI机箱。所有机箱均导入外部开始信号。您可以阅读高级定时与同步系统设计了解多机箱同步的更多信息。

图8. 多机箱的硬件同步

NI VeriStand在一个机箱内自动处理所有硬件同步,还可以导出或导入采样时钟和触发信号到其他目标上。

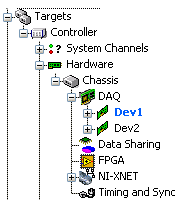

在NI VeriStand系统浏览器中将数据采集设备添加到系统配置后,您可以在图9中看到一个数据采集设备的名称用粗体显示。NI VeriStand自动选择了这个设备作为机箱的主数据采集设备。主数据采集设备接受外部触发信号完成多目标同步。NI VeriStand在单个机箱中将从数据采集设备与主数据采集设备进行同步,从设备不包含在多机箱同步中。

图9. 粗体显示的设备被选中作为主数据采集设备

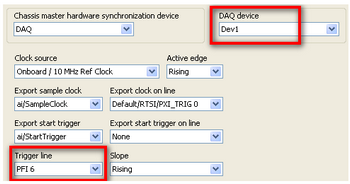

在机箱页面中,您可以定制主数据采集设备选择并进行触发。在树形结构中选择机箱。您可以看到如图10所示的页面,图中标出了对多机箱硬件同步而言重要的环节。

图10. 在PFI 6机箱中导入触发器

在图10中,机箱配置为在PFI 6的Dev1中导入触发器。查阅Dev1设备的硬件手册寻找PFI 6端子。

在创建这些配置并完成BNC与触发器排线之后,可以将它们部署到运行VeriStand的实时执行目标上来实现硬件同步。

如果您所使用的机箱没有CLK10 BNC接头,或是您需要更好的同步性能,您可以使用定时与同步板卡(NI-665x)实现相同功能。如果您决定使用NI-665x板卡实现这个功能,需要确定每个系统配置都添加了“10MHz PLL”定时与同步设备,而且配置为导入或导出10 MHz时钟。

软件同步

软件同步意味着系统中(在这个例子中是NI VeriStand实时引擎),不同代码块共享相同的执行时钟和一个开始信号实现在相同时间开始执行。

在适当的硬件设备可用时,NI VeriStand实时引擎被设计为使用硬件定时单点I/O(HWTSPIO)。HWTSPIO是一种数据采集软硬件特性,允许将软件执行锁定到物理硬件时钟上。将软件锁定到硬件只适用于模拟输入,因此即使不使用模拟输入通道,PXI系统配置中至少要包含一个模拟输入通道。

所以如果硬件采用如上同步方式,模拟输入通道会出现在每个配置中,每个目标的NI VeriStand实时引擎软件被自动同步。

参考时钟同步

在一些情况下,不仅要求系统组件相互同步,还要求同步到外部时钟参考。因为上述同步系统组件的方法包含主目标与分布式系统其他部分共享时钟和触发信号,参考时钟同步可以通过简单地将主目标连接到外部时钟参考实现。

NI VeriStand的Clock 10 Discipline附加组件让NI VeriStand引擎可以根据外部参考时钟进行同步。外部参考时钟可以是NI PXI-6682模块支持的参考之一。附加组件结合PXI-6682和其他定时与同步板卡,对PXI机箱按照外部参考时钟约束。您可以在这个页面了解关于这个附加组件的更多细节。

图11给出了相互同步并与外部时钟参考进行同步的分布式系统实例。

图11. 多机箱与外部时钟参考的硬件同步

结论

使用NI VeriStand,您可以配置实时I/O、激励档案、数据记录、警报和其他任务,通过从多个软件环境中导入模型实现控制算法或系统仿真,使用运行时间可编辑的用户界面快速构建可以和商用工具媲美的测试系统界面,使用NI LabVIEW、NI TestStand、ANSI C++/C++、.NET、Python和其他软件环境添加定制功能。

通过利用NI VeriStand 2010,您可以方便地创建分布式HIL、实时测试或是采用高效多目标特性监视系统。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)