1 概述 欢迎分享,转载请注明来源:内存溢出

随着数码时代的来临,除了PC外,越来越多的数码信息产品正在或即将进入我们的家庭:移动电话、掌上电脑、数码相机、GPS等等,这些产品越来越多的使用各种移动微存储器。这些存储器中很大部分是快闪存储器(Flash Memory)。

Flash memory是从EPROM和EEPROM发展而来的非挥发性存储集成电路,其主要特点是工作速度快、单元面积小、集成度高、可靠性好、可重复擦写10万次以上,数据可靠保持超过10年。国外从80年代开始发展,到2002年,Flash memory的年销售额超过一百亿美元,并增长迅速,预计到2006年,年销售额可达126亿美元/年。到目前,用于Flash memory生产的技术水平已达0.13μm,单片存储量达几千兆。

除大容量存储器应用外,Flash Memory也大量地替代EPROM、EEPROM嵌入到ASIC、CPU、DSP电路中,如TI公司的TMS320F240系列、TMS280系

列分别含有8K—128K Words的Flash Memory,又如Microchip公司,也推出了内嵌Flash Memory的16F系列MCU产品。

Flash Memory电路芯片设计的核心是存储单元(Cell)设计(包括结构、读写擦方式),外围电路都是围绕其设计。因此,我们首先要研究并确定电路中采用的Flash Memory Cell。Flash Memory从结构上大体上可以分为AND、NAND、NOR和DINOR等几种,现在市场上两种主要的Flash Memory技术是NOR和NAND结构。

本文分析了NOR和NAND结构的快闪存储器存储单元结构及其应用特点,给出了一种适合嵌人的改进型SSI存储单元结构,并对其的工作原理、性能、组成的存储器存储单元阵列、及可靠性设计进行了详细的分析。

2 存储单元结构

2.1 NOR存储单元

快闪存储器的擦写技术来源于沟道热电子发射(Channel Hot-Electron InjecTIon)与隧道效应(Fowlerordheim)。

NOR结构的Flash memory主要用于存储指令代码及小容量数据的产品中,目前的单片最高容量为512M,NOR Flash memory产品的主要领导者为Intel公司、AMD公司、Fujitsu公司、ST Microelectronics和公司。

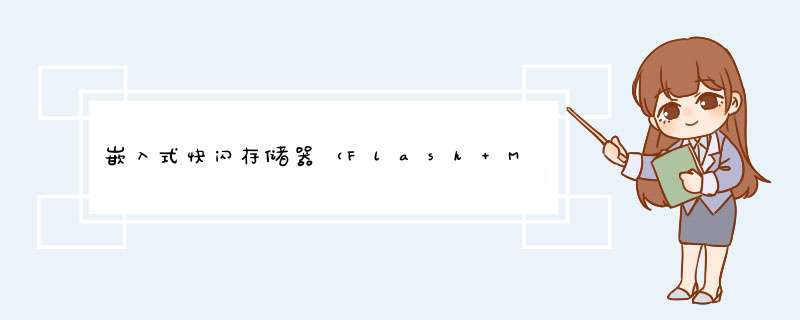

NOR结构的Flash memory采用NOR SGC(Stacked Gate Cell)存储单元,是从EPROM结构直接发展而来,非常成熟的结构,采用了简单的堆叠栅构造。图1是其结构原理图。浮栅的充电(写)是通过传统的沟道热电子发射(CHEI)在漏端附近完成的;浮栅的放电(擦除)在源端通过隧道氧化层的隧道效应来实现。

该结构的特点是单元面积小,同EPROM的面积相当,编程(写)时间短,在10μs左右,源漏结可以分开优化,漏结优化沟道热电子发射,源结优化隧道效应,采用了自对准工艺。

随着制造技术的进步,存储单元的特征尺寸越来越小,工作电压降低,带来的负面影响是热电子发射效率降低,编程时较难工作于4V漏源电压下。为提高热电子发射效率,需要对源结、漏结、沟道掺杂分布进行优化1,整体工艺较复杂,编程电流也较大,大约400μA/bit(0.5μm)技术。工艺流程以0.25μm-0.35μm产品为例,采用DPDM制造的快闪存储器需要23块Mask版,进行27次光刻。

2.2 隧道效应存储单元

隧道效应存储单元是目前快速发展的快闪存储器生产技术,在快闪存储器中一般组成NAND存储阵列,单元面积小,其工艺较简单,容量大,成本低,适用于低价格、高容量、速度要求不高的Flash memory客户用于数据存储;在MP3、PAD、数码相机、2.5G及3G无线系统中得到了广泛的应用。NAND快闪存储器产品的生产工艺已达到0.13μm,单片电路的存储容量超过1Gb。

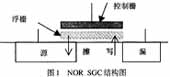

图2是隧道效应存储单元结构原理图,其编程、擦除通过隧道氧化层的隧道效应来实现,类似EEPROM,其优点是在编程时可以工作在2.5V的源漏电压下,功耗低,非常适合非接触式IC卡,同时NAND阵列的单元面积是NORSGC单元面积的二分之一,适合于大容量集成。

隧道效应存储单元擦写工作电压高,一般要求达到16V-20V,对器件、电路的设计要求高,编程(写)时间较长,在50μs-100μs,不适合字节编程,适用于大容量页编程,像EEPROM一样,编程时,加在隧道氧化层上电场强度高,存在SILC(stress induced leakage currents)效应,对工艺要求高。

2.3 源侧热电子发射(SSI)存储单元

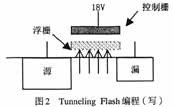

在九十年代初,报道了SSI(Source-Sidehotelectron InjecTIon)存储单元,结合了NORSGC单元的快速编程与隧道效应存储单元编程功耗低的特点,其原理为split-gate concept2,图3是其编程原理。

SSI存储单元浮栅的充电(写)是通过沟道热电子发射,在源端附近完成的;浮栅的放电(擦除)在漏端通过隧道氧化层的隧道效应来实现。在编程(写)过程中由于部分沟道由CG栅(1.5V)控制,改进了NOR SGC单元的编程(写)电流大、优化了沟道热电子发射效率,编程时的源漏电压可低至3.3V。其存在的问题是必须在数据线译码中使用大量高压开关,电路设计复杂,沟道热电子发射没有完全优化、读出电流小、工艺也比较复杂。

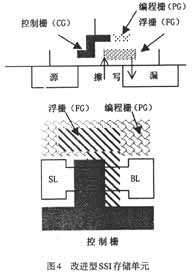

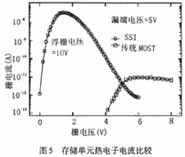

图4是我们采用的、也是本文主要讨论的改进型SSI结构的存储单元结构,在存储单元中增加了编程栅来提高CHEI效率(效率的提高见图5)。其优点有工艺简单,只要在数字CMOS逻辑电路的基础上增加三次光刻(高压NWELL、高压MOS管选择氧化、Fowler-Nordheim N+埋层注人)就能完成整个电路工艺制造,易于嵌入到普通ASIC电路中;Flash Cell源漏电压在3.3V就能完成编程工作,简化电路设计;编程速度快,0.5μm Flash Cell源漏电压在5V的情况下,编程时间优于500ns,在3.3V下小于10μs,非常适合嵌人式电路设计。

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)