目前高性能集成电路方面正在发生的架构改变将影响半导体产品的方方面面,包括从设计到终测和封装。这一变化背后的驱动因素有两个:(1)不断增加的数据带宽需求;(2)功率管理方面的需求。这两方面的需求正在驱使设计师对出入IC的数据传输方式作出根本的改变。

设计工具和制造工艺已经改进到可用逻辑门数量已经不再是片上系统(SoC)性能的限制因素了。相反,性能限制因素主要是向芯片“内核”传送数据的速度,以及功率管理和热管理。过去,可以通过增加并行总线带宽来传送较大的数据量,但这种方法在功耗、引脚数量、封装以及PCB成本等方面都有缺点。

实际上由于互联层之间的电容和电感特性,在现有的并行总线上传输高速数据时还面临一些其它限制。当线上的数据率高达约1Gbps时,上升时间、抖动、通道间和分布式时钟摆率特性等这些并行总线设计中固有的问题将开始成为关键的限制因素。

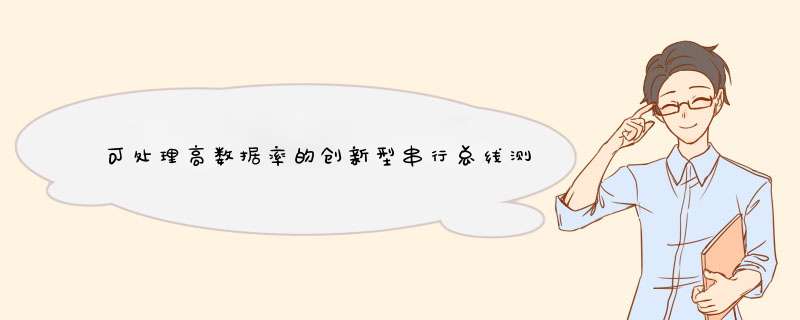

这些限制因素激励着数据通信领域的数字设计工程师门在十年前就开始考虑串行技术。通过在为数不多的串行信道(图1)上实现非常高的数据率,他们发现数据量和功率预算要求都能得到满足。高速串行总线(HSSB)的很多物理性能与并行总线不同。主要的差别包括:

对于发送和接收等量的数据来说所需的连接点数量更少

串行总线为点对点连接,而传统的并行总线则是多点对多点连接

串行总线为单向的数据通道,而传统的并行总线则是双向

串行总线的电压摆幅小,可以支持更高速率的数据传输

串行总线采用差分信号,克服了影响低电压摆幅的共模噪声

与传统的并行方式相比,串行的定时和数据捕获方式有根本不同

图1:采用高速串行总线的PC架构。

高速测试方面的挑战

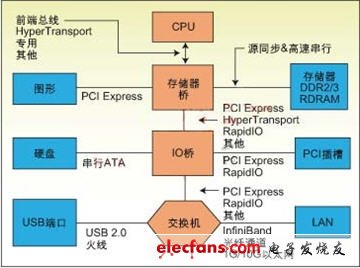

在以不是太高的成本通过HSSB提供这些呈指数式增长的传输速率方面测试公司将扮演关键的角色。像PCI Express I和II、HyperTransport 2.0和3.0、XAUI、XDR、RapidIO以及 InfiniBand这些高速接口将被越来越多地用来提供更高的数据率(图2)。但是,高速数据总线带来了一些很大的测试挑战,在这里,传统的功能测试和简单的可测性设计(DFT)方法学不再适用。在高端自动测试设备(ATE)平台上的传统“功能”测试流程能够提供很全面的测试覆盖,但这些经过生产验证的方法存在较大的缺点,比如成本较高,测试编程复杂。此外,每个引脚的成本随着高速数据应用中总线速率的升高而升高,这也使得传统的功能测试方法渐不可行。

图2:到2010年数据率将超过10 Gbps,因此测试行业需要创新的测试方法来克服高速总线方面的挑战。

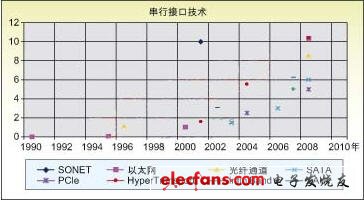

于是制造商们又转向能够实现更全面和成本优化的高速总线测试的环回技术(即:利用设备本身提供测试数据然后接收返回到设备的数据进行确认)。图3 给出了一个简化的PCI Express通道以及可能不同的环回位置,从有助于晶圆探测的纯内部环回点,到被测器件(DUT)外面的环回位置。环回测试非常有效,不过实现的方式也非常重要,因为要考虑高速信号的典型损耗预算。损耗预算决定了可接受的信号劣化的程度,它通常需要考虑三个因素,即发射器,接收器和内部互联,所有这几项都将劣化信号的“眼图”,从而影响测试覆盖率。

图3:在简化的PCI Express单通道中可能的环回位置。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)