引言

第三代移动通信的概念形成了三大主流标准,即欧洲与日本提出的WCDMA、美国提出的CDMA2000和中国提出的TD-SCDMA。TD-SCDMA是由中国无线通信标准化组织(CWTS)提出并得到ITU通过的3G无线通信标准。TD-SCDMA是由中国无线通信标准化组织(CWTS)提出并得到ITU通过的3G无线通信标准。

设计及其实现

1 信令数据采集卡设计思路

本卡主要是根据协议的选择来完成七号信令数据的采集。本卡基于PCI设计,完成的主要功能有:物理层的数据采集、HDLC链路控制。在整个系统中主要完成层一和层二的控制,它要求较高的可靠性、可用性和可扩展性。为了满足网络测试仪数据流量大、方便用户使用的特点,我们选用了自带标准PCI协议规范的HDLC控制器(MindSpeed Bt8474)、专用的E1/T1/J1成帧器(MindSpeed Bt8370)芯片和Windows 2000作为此卡的基本软硬件架构。每块板卡可以实现8收4发,软件驱动基于PCI的框架,能满足快速的数据采集要求,性能稳定。

2 芯片资源简介

本卡采用的主要的芯片是MindSpeed公司的自带PCI总线规范的多通道同步网络控制器(MUSYCC)Bt8474和E1/T1成帧器Bt8370。

● PCI总线简介

PCI的含义是周边器件互连。PCI总线是一种不依附于某个具体处理器的局部总线,基于PCI的系统不受处理器升级的影响。每个典型的PCI可以支持大约10个电气负载。它支持32位或64位的总线宽度,支持的工作频率为33MHz或66MHz。工作在33MHz/32位时,理论上最大数据传输速率能达到133MHz/s。

● Bt8474简介

BT8474 是一个多信道同步通信控制器(MUSYCC),它能支持128个数据信道,每个信道根据配置可以支持“HDLC、SS7、透明传输”三种协议。在数据处理中主要完成层2(数据链路层)的处理。

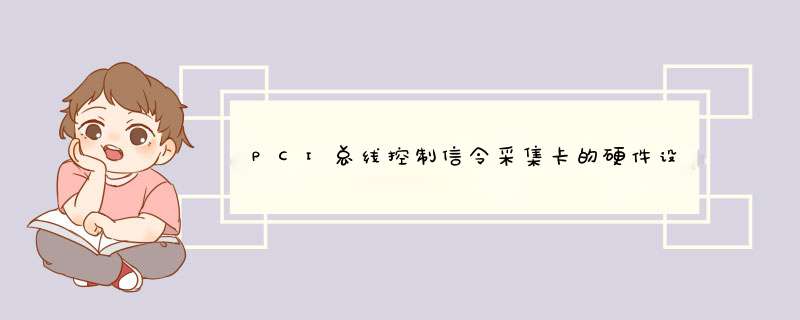

其功能框图如图1、图2所示。

图1 Bt8474功能框图

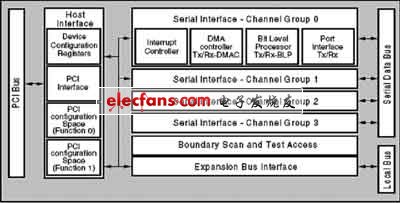

图2 Bt8474的串口功能设计原理图

● Bt8370简介

BT8370是一个T1/E1收发成帧器,支持的收发接口的Line Rate为 1.544Mb/s(T1)或者2.048Mb/s(E1)。物理线性接口电路恢复来自电缆的“+3dB到-43dB”的模拟时钟和数据。

BT8370主要由以下几部分组成:

(1)微处理器接口(MPU):主要完成和其他设备之间的通信控制。

(2)接收/发送线性接口单元(RLIU/TLIU)。

(3)数字发送器(XMTR)。

(4)数据接收器(RCVR)。

(5)发送系统总线(TSB)。

(6)接收系统总线(RSB)。

(7)时钟速率适配器(CLAD)。

(8)边界扫描接口(JTAG)。

其功能图如图3、图4所示。

图3 Bt8370的功能框图

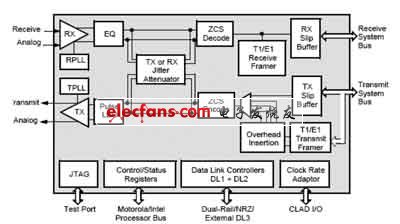

图4 Bt8370的设计原理图

3 信令采集卡硬件实现

图5是信令采集卡的总体设计框图。

图5 E1采集卡的总体设计框图

采集卡从E1线上采集七号信令消息(也包括一号随路信令),用以监视和仿真整个通话流程。PCI接口芯片(HDLC控制器)是一个多功能设备,包括一个网络控制器和一个PCI桥设备(EBUS)。网络控制器用以控制时隙映射,配置DMA传输;PCI桥设备用以选通和配置成帧器,其中成帧器的选通是通过一个CPLD来完成的。另外,网络控制器和PCI桥设备的中断是分开的,分别通过INTA和INTB上报PCI控制器。信令信号经过成帧器成帧后,通过HDLC控制器以DMA方式送入到PC缓冲区;用户可以通过驱动提供的接口函数到缓冲区取信令数据进行分析。

根据TD-SCDMA网络测试仪表的总体设计方案要求,七号信令卡作为PCI插槽的板卡,通过高阻适配器采集E1信号,给8370成帧处理后,通过串口送给8474,完成消息的重组后,把消息送给上层软件进行协议分析处理。七号信令卡的硬件结构提供网络接口的物理层和部分链路层功能,由软件来实现物理层和链路层的数据控制和部分应用层的功能。本卡可以同时完成8路监测、4路仿真。

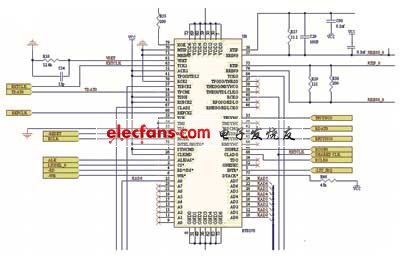

按照任务目标要求,七号信令卡主要由以下硬件单元组成:HDLC逻辑层Bt8474、PHY物理层Bt8370、CPLD逻辑控制、高阻适配器、DB15、变压器等。图6是E1采集卡的硬件结构。

图6 E1采集卡的硬件结构

本文作者的创新点:

(1)本卡在硬件设计上,通过时隙和通道复用,把只有四个串口的8474扩展实现了8路串口。

(2)利用本信令采集卡可以实时监测通信链路的建立、传输、停止等过程,

(3)可以通过该卡的信令发送功能,实现业务仿真,减小TD-SCDMA网络设计风险。

(4)现场测试证明,本信令采集卡完全可以应用于TD-SCDMA网络测试。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)