引言

CPCI规范是由PICMG制定的一种开放工业计算机标准,用于工业和嵌入式应用。CPCI系统背板和CPCI板卡采用标准的2mm高密度气密性针孔连接器,提高了系统可靠性。CPCI可采用IEEE 1101.11后端输出方式,使系统维护更加便捷。

CPCI板卡的尺寸分3U(100mm×160mm)和6U(160mm×233mm)两种,3U系统只提供32位/64位的PCI系统总线,6U的系统除了提供32位/64位的PCI系统总线外,还通过连接器接口J3、J4、J5实现自定义总线,可用作高速数据通信或通用输入/输出线等,适用于数字化高速处理的模块化设计应用。

本文利用TMS320C6416T内部集成的32位、33MHz PCI主/从接口,给出了6U的CPCI信号处理板卡设计方案,并对其软件设计特别是DSP的二次引导程序做了说明。

硬件设计

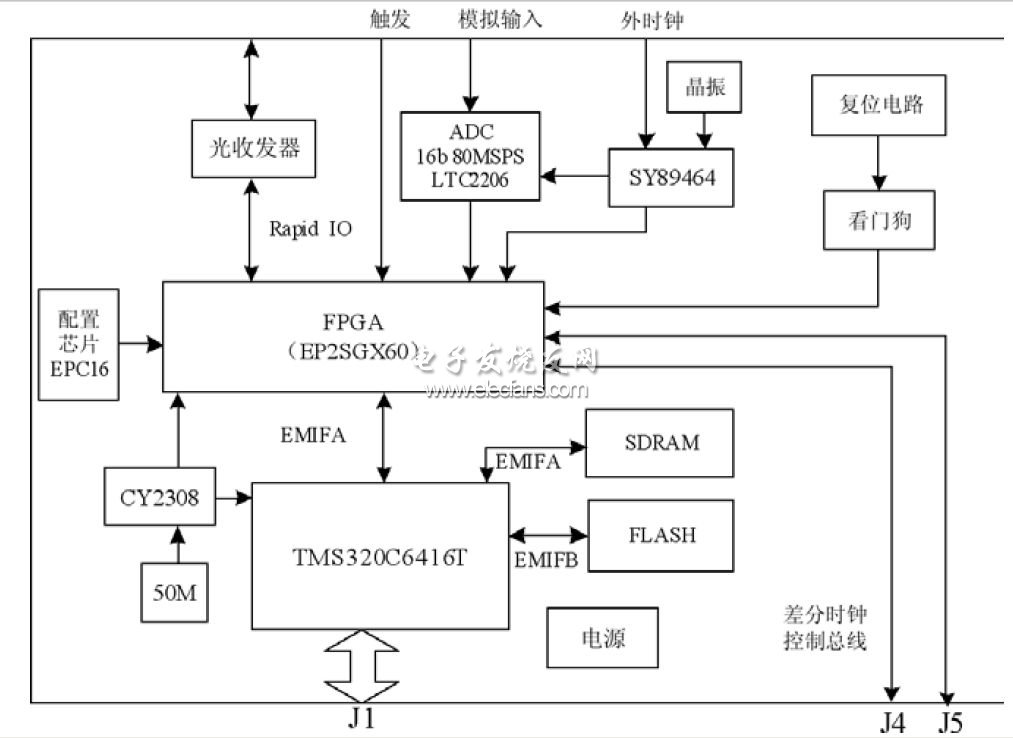

CPCI板卡有J1~J5五个连接器接口,其中只有J1是必须有的,为32位PCI信号接口。J2为64位扩展PCI信号。对于主控板以外的CPCI板卡,J3、J4、J5可用作用户自定义接口。本文所设计的CPCI板卡使用J1、J4、J5接口,主要由DSP、FPGA、SDRAM、FLASH等组成。板卡以TMS320C6416T为核心,通过高性能FPGA实现AD数据采集后的预处理,然后经64位宽的EMIFA总线传入TMS320C6416T中进行数字信号处理,处理数据可通过32位PCI总线、光收发器或CPCI自定义总线传输至外部设备。CPCI的J1接口为32位、33M的PCI接口信号,与TMS320C6416T的PCI外设连接。DSP通过EMIFA的CE0存储空间连接4片SDRAM芯片MT48LC32M16A2,扩展成64位宽度的128MB存储器,CE1、CE2空间连接FPGA,通过J4、J5扩展。EMIFB的CE1空间通过FLASH芯片S29LV016D扩展2MB的FLASH,用于系统的自举。系统框图如图1所示。

图1 CPCI板卡框图

处理板通过高速16位ADC芯片LTC2206实现模数转换,然后将数据传输到FPGA进行数据预处理,包括数字下变频及缓存等,之后经64位EMIFA总线通过EDMA传到DSP中进行数字信号处理,最后通过CPCI总线传输到主机。板卡通过带选择器的时钟分配器SY89464实现内外时钟的控制和单端时钟到差分时钟的转换。FPGA的配置芯片采用EPC16,配置方式为PS,EPC和FPGA通过JTAG链实现编程。

TMS320C6416T通过SDRAM扩展256MB存储空间,SDRAM采用512Mb芯片MT48LC32M16A2,位宽为16位,通过4个此芯片扩展为64位。

EMIFB的CE1空间通过FLASH扩展BOOTROM空间,采用FLASH芯片S29AL016D实现,S29AL016D有8位byte和16位word两种方式,通过引脚byte#设置,这里使用8位数据格式。

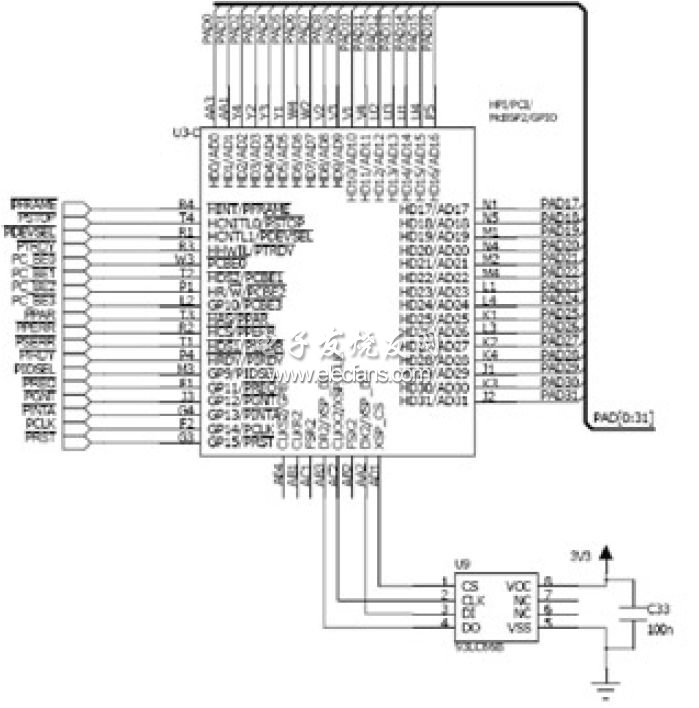

PCI接口信号的连接如图2所示,使能TMS320C6416T的PCI接口对应PCI_en引脚置高。该接口符合PCI 2.2规范,为33M、32位的PCI主/从接口。

图2 TMS320C6416T的PCI接口电路图

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)