引言

随着图形处理的巨额运算量,CPU变得不堪重负。此时,需要使用特定的硬件设备来为嵌入式CPU承担图形处理的任务。

具有三维图形硬件加速能力的ARM+FPGA架构嵌入式图形系统就是其中一种解决方案。其中,ARM处理器负责运行嵌入式 *** 作系统、执行上层图形应用程序,而三维图形处理所需的大量运算则由FPGA实现的GPU(图形处理单元)进行。

图形API简介

在图形系统中预先定义了一组图形API,作为一个抽象层将图形应用程序和图形系统的具体实现隔离开来。具体的图形应用程序都将通过这些图形API来完成所有与绘制图形相关的工作。这样,同样的应用程序就可以在不同的目标图形系统上运行。

目前应用较为广泛的标准图形API主要有Direct3D和OpenGL。OpenGL定义了与具体硬件实现无关的软件接口,并且不受制于具体的窗体系统。

本文选用23条OpenGL中最常用的API作为本系统的图形API。在执行应用程序时,具体的图形API被转换成GPU可以处理的渲染列表数据格式,从而将计算任务转交由GPU完成,实现对三维图形处理的硬件加速。

系统硬件设计

系统硬件结构

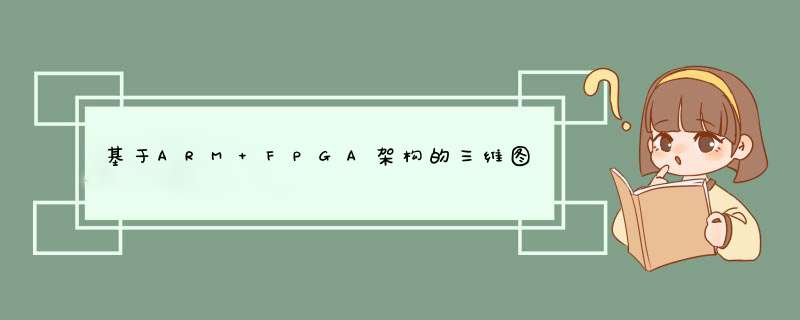

本文设计的嵌入式图形系统由基于ARM处理器的最小系统、FPGA实现的图形加速、LCD控制器等功能模块,以及常用外设接口电路组成,如图1所示。

图1 系统硬件结构

基于ARM处理器的最小系统是本系统的核心模块,主要由嵌入式处理器、系统内存SDRAM和FLASH存储器组成。SDRAM为处理器运行 *** 作系统和执行应用程序提供内存空间,FLASH用来存放系统引导代码、 *** 作系统内核和应用程序。

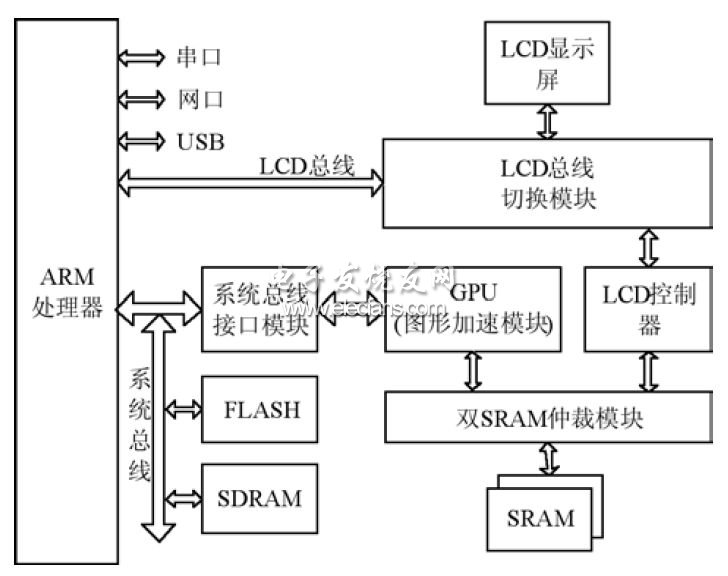

图形加速模块是使用FPGA实现的嵌入式GPU,是系统能够实现硬件加速的关键部件。它通过内部图形处理流水线处理CPU生成的渲染列表,并最终形成像素数据写入帧缓冲SRAM中供LCD进行显示。该模块在三维图形处理中使用固定功能的图形处理流水线,如图2所示。

图2 图形处理流水线示意图

图形加速模块在一片SRAM中生成完整帧数据后将其控制权交给LCD控制器,并使用另一片SRAM继续下一帧数据的计算。在新的一帧数据完成后便再次与LCD控制器交换控制权。LCD控制器通过SRAM仲裁模块从当前显示的帧缓存中读出帧数据,生成符合LCD显示屏要求的时序,完成三维数据的显示。

系统中存在两组LCD总线。一组是ARM处理器提供的LCD总线,用来显示嵌入式 *** 作系统的图形用户界面;另一组是进行三维图像显示的LCD控制器的LCD总线。总线切换模块负责两类总线的切换,将合适的LCD总线挂接到LCD屏上进行显示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)