介绍了嵌入式PowerPC 处理器MPC8280 和多通道控制器的主要特征。MPC8280 具有8 个TDM 接口,每个TDM 均支持E1/T1 接口。多通道控制器可以使MPC8280 最多支持256路独立的HDLC 或者透明传输通道。通过多通道控制器可以方便地实现时分复用数据的复用和解复用。本文重点研究了多通道控制器的数据结构组织方式及驱动程序的实现过程,给出了主要功能函数的设计流程,并在VxWorks5.5 *** 作系统上进行了综合测试。

1 MPC8280 处理器特性及MCC 概述

MPC8280 是一款集成了高性能的PowerPC? RISC 微处理器和诸多外围通信控制器的多用途通信处理器,在通信和网络系统有较为广泛的应用。

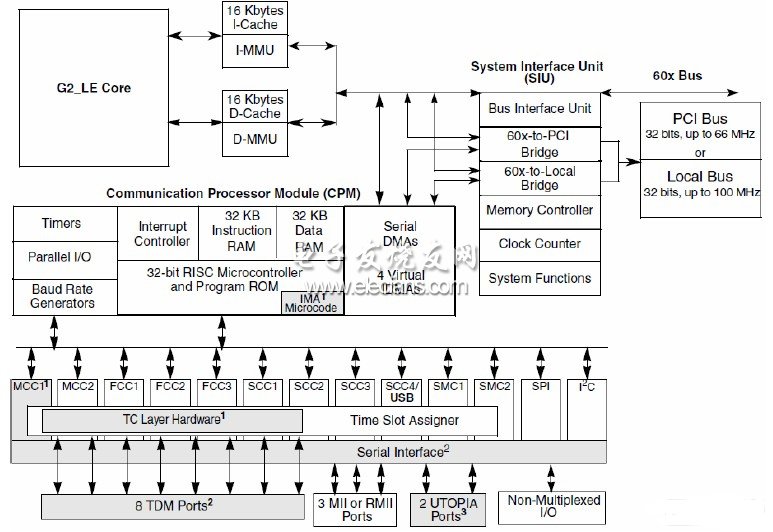

MPC8280 模块组成如图1 所示。其中,G2_LE 内核是MPC603e 微处理器的嵌入式版本,具有16KB 的指令缓存和16KB 的数据缓存;系统接口单元SIU 主要完成系统复位、中断管理、时钟配置、总线接口及内存控制等功能;通信处理模块CPM 包括一个32 位的RISC 处理器CP,三个全双工的快速串行通信控制器FCC,两个多通道控制器MCC,四个全双工的串行通信控制器SCC,两个全双工的串行管理控制器SMC,SPI 接口,I2C 总线控制器等。时隙分配器可将SCC、FCC、SMC、MCC 的数据复用到八个时分复用接口TDM。

图1 MPC8280 模块结构图

MPC8280 有两个具有时隙分配器的串行接口,分别为SI1 和SI2。每个SI 有四个时分复用接口。SI1 和SI2 分别对应为TDMa1,TDMb1,TDMc1,TDMd1 和TDMa2,TDMb2,TDMc2,TDMd2。SI 可以根据SIRAM 的配置将TDM 的某一时隙路由到特定的接口(如TDMa1 的第2个时隙到MCC1 的第3 个通道,TDMb2 的第1 个时隙到FCC1 等)。

一个MCC 可以支持最多128 路独立的时分串行通道。MPC8280 具有两个MCC,每个MCC连接到一个SI。MCC 的数据流可以通过SI 的四个时分复用接口TDM 中的任何一个进行数据传输。

一个MCC 中的128 个通道以32 个为一组连接到某一个TDM 接口上。MCC1 的通道(0-127)只能连接到SI1 上,MCC2 的通道(128-255)只能连接到SI2 上。MCC 的每一个通道都可独立配置为不同于其它通道的工作模式。通过配置SI 和SIRAM 可以将TDM 数据中的时隙路由到特定的MCC 通道。

每个MCC 都具有以下特性:最多达128 路独立的HDLC 或者透明传输通道,或者64 路SS7 通道;独立的发送和接收路由;每一通道都可支持HDLC、透明传输或者SS7 协议。

2 MCC *** 作概述

MPC8280 的内核G2_LE 和外部的通信是由CPM 来完成。CP 根据相应的接口控制寄存器配置来执行数据发送或接收 *** 作, *** 作完成后再向G2_LE 内核的中断寄存器写入中断值。

G2_LE 内核根据中断值调用相应的中断处理函数,由此完成数据交互过程。

每一个MCC 能通过相应的SI 连接到TDM 接口上。一旦SI 的某个TDM 被配置为包含有MCC 通道的时隙并且TDM 开始工作,CP 就将MCC 通道发送缓冲区内的数据复制到发送FIFO内,然后SI 在时钟驱动下将MCC 通道的发送FIFO 内数据发送到TDM 接口上,或者将数据从TDM 接口上接收下来并存入到MCC 通道的接收FIFO 内,然后CP 再将接收FIFO 内的数据复制到MCC 通道的接收缓存区内。

CP 通过一系列与MCC 相关的数据结构来实现对MCC 通道FIFO 的管理。MCC Globalparameters 管理着MCC 模块的各个通道,以及 *** 作这些通道所用到的门限参数和基址指针的配置。每个通道还有一组channel-specific parameters 和channel-extra parameters,包含了该通道的协议状态信息和指向该通道的接收及发送缓存描述符的指针。

Channel-specific parameters 会因该通道所工作的协议不同而作不同的解释。如果TDM的配置含有MCC 超通道(super-channel)时隙的话还要用到超通道表(Super-channelTable)。

● global Parameters MCC1 的global parameters 适用于通道0—127,MCC2 的global parameters 适用于通道128—255,分别位于相对于DPRAM 基址偏移0x8700 和0x8800 处。

●Channel-specific Parameters 这些参数仅局限于相应的MCC 通道,位于相对于DPRAM 基址偏移64×CH_NUM 处。

● Channel Extra Parameters 包含相应通道缓存描述符的基址和指针。位于相于对DPRAM 基址偏移XTRABASE+8×CH_NUM 处。其中XTRABASE 是MCC Global Parameters 之一。

● Super-channel Table 仅当在SIRAM 中配置了超通道时使用。位于相对于DPRAM基址偏移SCTPBASE 处。其中SCTPBASE 是MCC Global Parameters 之一。由于我们的应用场合未使用到超通道,所以未对该参数进行配置。

● BD Tables 位于外部存储器。接收通道的缓存描述符表位于相对于DPRAM 基址偏移MCCBASE+8×RBASE 处。发送通道的缓存描述符表位于相对于DPRAM 基址偏移MCCBASE+8×TBASE 处。MCCBASE 是Global Parameters 之一,RBASE/TBASE 是Channel Extra Parameters之一。

● Interrupt Queues 位于外部存储器。共有一个发送中断表和一至四个接收中断表。TINTBASE 指向发送中断表,RINTBASE指向接收中断表。TINTBASE 和RINTBASE均为Global Parameters。

3 MCC 驱动的设计与实现

该驱动运行在嵌入式 *** 作系统VxWorks5.5 之上,开发环境为Tornado 2.2.1 for PPC。

MCC 驱动主要分为以下几部分:

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)