本文实现了DDS正弦信号的发生,限于CPLD的128宏单元不够用也不知道怎么优化,后来就干脆把按键、频率显示、频率控制字交给单片机控制产生,再由单片机讲频率控制字传送给CPLD,这样就实现了频率的控制。最终产生的正弦信号频率范围为1HZ~30KHZ,频率可步进1HZ也可通过单片机预置,也可以自动扫频信号。起先出来的频最大误差达到2HZ多,觉得不对劲出来的频率应该很精确不会有这么大的误差,后来发现原来是晶振不准有点误差,后来经程序修改使输出最大频率误差在0.1HZ以内,经过这几天的努力总算感到了一点的欣慰。

这是VHDL顶层模块:

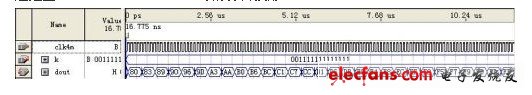

这是当k=001111111111111时的仿真波形:

单片机控制6个数码管显示当前的频率,P1口接4个功能按键,分别是+、-、选择和扫频,再用两片574向CPLD输出频率控制字。限于时间暂时做到这么多。

由于是用DAC0832转换的(转换时间1us)所以晶振就限制在1M之内了,出来的最大频率,根据奈奎斯特采样定理也就限制在0.5MHZ之内了(不过失真很大的,取小点好了),最后对出来的波形再做滤波就可以了。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)