DM816x,C6A816x,AM389x是TI新一代高性能SOC,系统集成度高,系统控制模块化,架构与以往TI SOC平台有所不同,本文针对最小系统的时钟配置,电源管理,内存映射,内存配置的区别做深入解释。

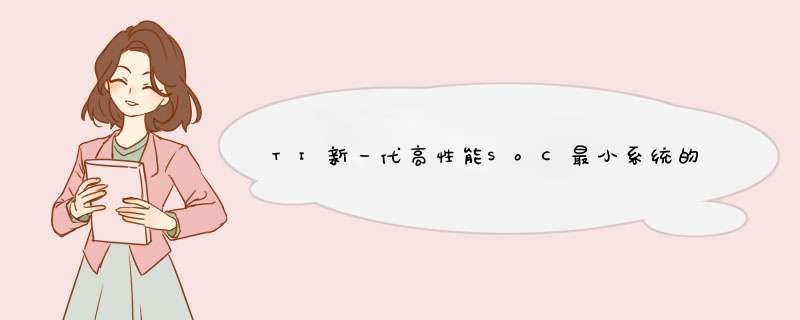

DM816x,C6A816x,AM389x引脚兼容(为方便讨论,下面统称DM816x),资源配置主要区别如下表所示,这种兼容系列产品便于用户基于同一平台,根据不同的产品需求选择合适的型号,可以节省大量的硬件、系统软件开发时间。

表1. DM816x, C6A816x, AM389x比较表

1.时钟配置

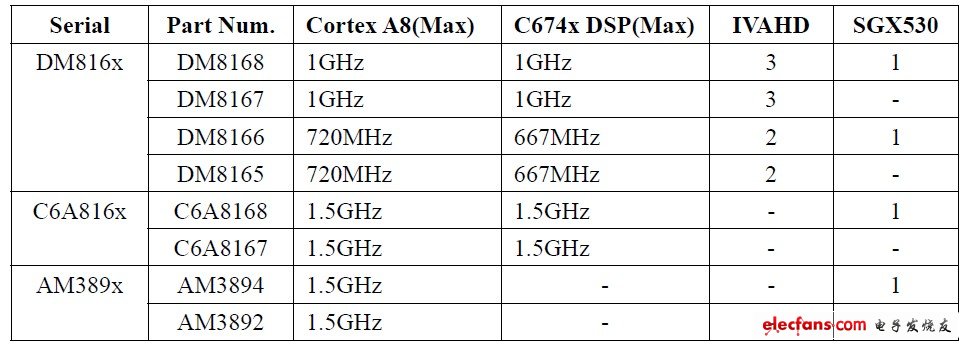

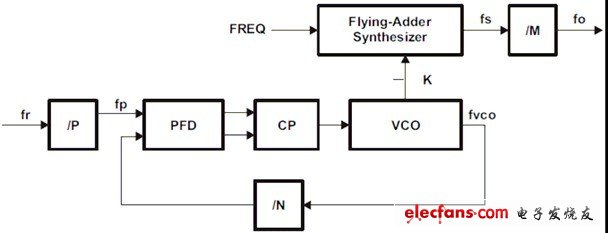

DM816x内部有4个FAPLL(Flying Adder PLL,结构见图1.1),分别负责不同模块的时钟配置,系统时钟框图见图1.2。

图1.1 Flying-Adder PLL框图

图1.2 DM816x系统时钟结构图

FAPLL相对于传统的PLL具有精度高,响应快,减少模拟电路复杂度等优点,更适合于音视频应用。从使用者的角度在DM816x上最直接的体现是它支持小数分频系数,方便于产生需要的频率。

每个FAPLL结构由两部分组成:

1. MulTIphase PLL。

2. Flying Adder Synthesizer.(可能有多个为不同模块提供不同频率的时钟)

FAPLL的配置属于Control Module的PLL部分。

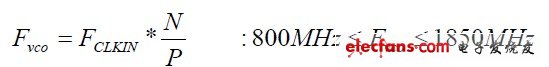

MulTIphase PLL的配置寄存器为相应的FAPLL控制寄存器,对应四个FAPLL分别为:MAINPLL_CTRL,DDRPLL_CTRL,VIDEOPLL_CTRL,AUDIOPLL_CTRL.Multiphase PLL的输出时钟频率为:

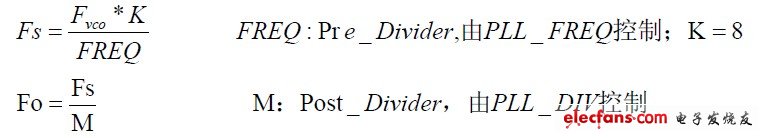

Flying Adder Synthesizer的配置寄存器为相应FAPLL的PLL_FREQ和PLL_DIV寄存器,可能有多组对应多个Synthesizer.对应图1.1中Fs和Fo的输出频率计算公式为:

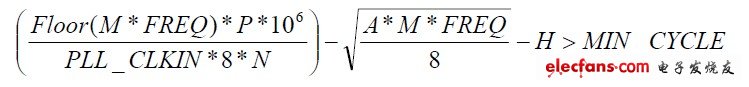

FAPLL的配置参数不能任意选择,在根据上述公式计算频率的基础上需要满足下面公式的条件:

● A = 169 (如果AUDIOPLL的输入源是从MAINPLL输出的,则AUDIOPLL的A=218)。

● H = 10 (如果M*FREQ是8的倍数,否则H=0)。

●800MHz≤PLL_CLKIN*N/P≤1600MHz?? 10MHz≤PLL_CLKIN/P≤60MHz

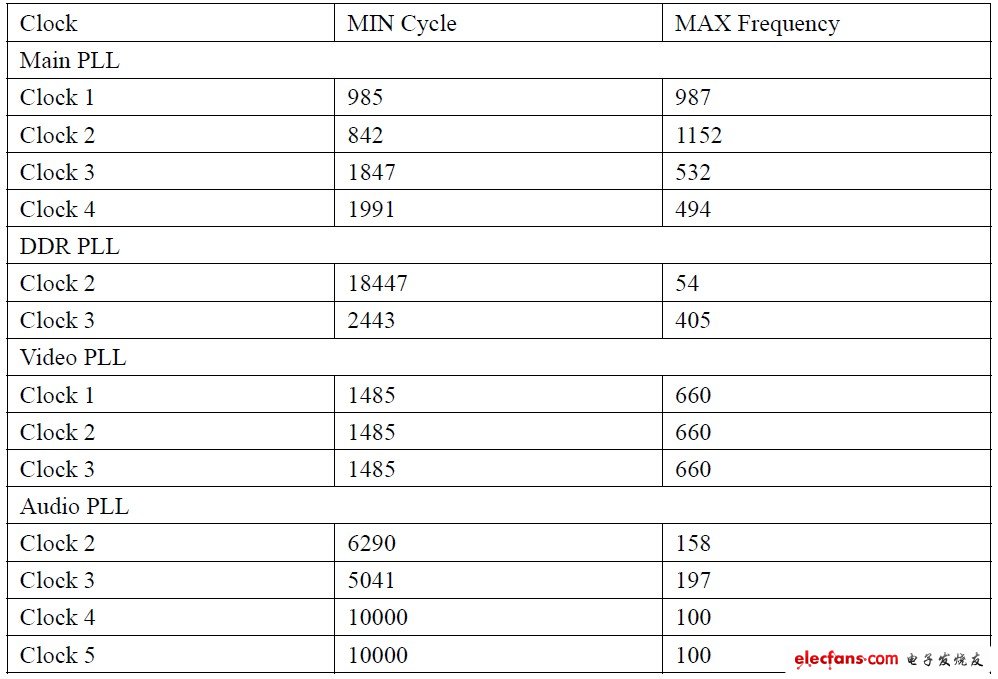

● MIN CYCLE见表2

表2 PLL时钟频率

针对视频应用,系统输入时钟CLKIN=27MHz,在EVM板提供的gel文件,UBOOT代码里有提供合适的FAPLL配置参数。对于其它的输入时钟频率,需要根据上面的条件计算合适的配置值。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)