Tsu/Tco 在Quartus II 的报告中有两种不同含义.

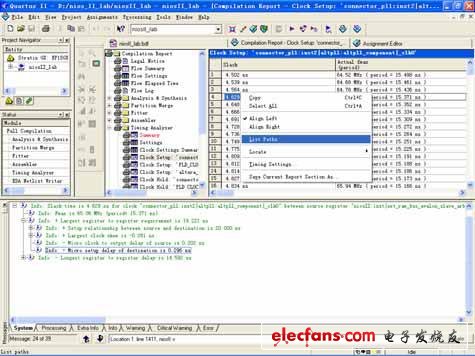

1. 片内的Tsu/Tco 是指前级触发器的Tco 和后级触发器的Tsu, 一般来说都是几百ps 级别的. 可以通过“List Paths”命令查看。这里的Tsu/Tco 主要由器件工艺决定, 工作时在受到温度,电压的影响略有变化.(如下图所示)

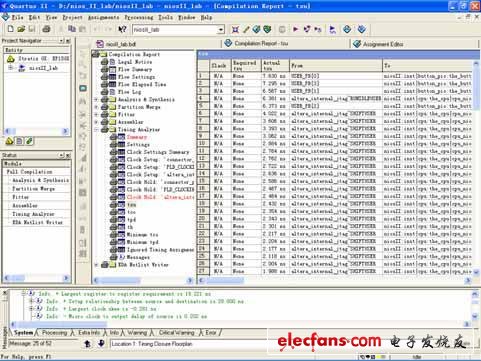

2. 管脚上的Tsu/Tco 它是保证系统Famx 重要的TIming 元素(如下图示). 比如: 两个芯片之间工作在100MHZ, 因为100M 的周期为10ns, (现忽略PCB 走线的延迟), 如果某信号对FPGA 来说是输入, 那么前级芯片的Tco 加上FPGA 的Tsu 就不能够超过10ns. 如果某信号对于FPGA 来说是输出,那么FPGA 的Tco 加上后级芯片的Tsu 也不能够超过10ns. 只有这样,才能够保证片间通信正常。因此对FPGA 的管脚进行适当的Tco/Tsu 的时序约束,是至关重要的TIming 设计技巧.

管脚上的Tsu/Tco 分为以下三个部分.

1) IOE 走线的延迟. 这个延迟在管脚的Tsu/Tco 延迟中占有相当的比例,Altera 的器件为了降低Tsu/Tco 在IOE 上的延迟, 专门在IOE 中设置了两种类型的触发器, 即 : Fast Input register(FPGA 的管脚为输入时,优化Tsu), Fast Output Register(FPGA 的管脚为输出时,用于优化Tco)

2) 内部逻辑走线的延迟。在Altera 的FPGA 中, 由若干个基本资源LE 构成一个LAB,比如: StraTIx Gx 是10 个LE 组成一个LAB. LAB 横向和纵向排列形成阵列. 在FPGA 中,以LAB 为基本单元, 根据走线长度的不同,分为C4(表示横跨4 个LAB 的走线资源),C8,C16,R4,R8,16,R24 等不同的走线资源,不同的器件支持不同的走线资源。

3) 触发器的Tsu/Tco 的需求,这里的Tsu/Tco, 这是由器件工艺决定的,最小的Tsu/Tco 的要求. 在实际的工作环境中,受温度,电压的变化有微小的变化.

前面提到:对FPGA 的管脚进行适当的Tco/Tsu 的时序约束,是至关重要的TIming 设计技巧.关键是在出了问题的时候,怎么去解决?

Quartus II 有四处可以对Tsu/Tco 进行约束.

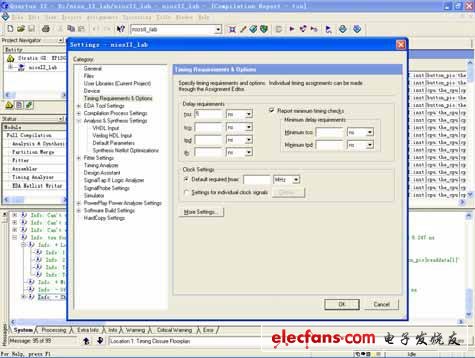

1. 全局时序约束. 在Quartus II 中执行Assignments..Timing Setting d出如下界面.设计者可以根据系统Fmax 的要求去约束Tsu/Tco.

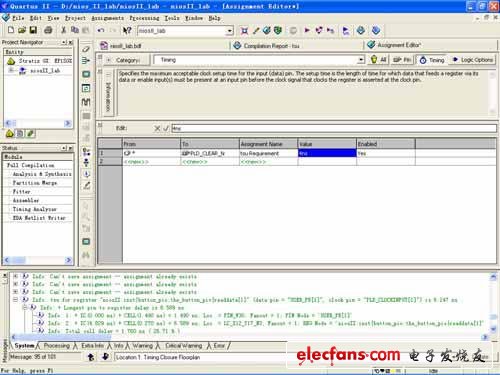

2. 执行Assignments..Assignment Editor 命令,得到如下界面.设计者可以根据本设计的要求,对输入/输出管脚设置Tsu/Tco 的约束;也可以约束内部触发器的Tsu/Tco 的值。(如下图所示)

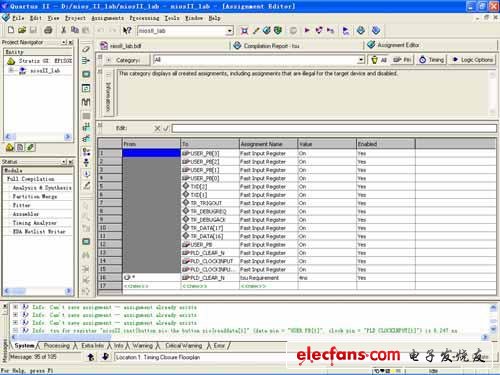

3.执行Assignments.. Assignment Editor 命令,选择”All”或者”Logic Options” ,对管脚进行Tsu/Tco 的约束.

在”To” 选择对应的管脚,在Assignment Name 中选择”Fast Input Register” 来约束Tsu, 选择”Fast Output Register” 来约束Tco. 这也是逻辑工程师通常说的: 为减少Tsu/Tco 的值,放到IOE 中.

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)