摘要:定时同步是高速数据传输的关键技术也是难点问题。在对锁相环数字化设计、DDS原理结构和参数设计进行研究的基础上,提出了一种基于DDS的高速定时同步方法,对该定时同步方法的原理结构框图进行了详细的论述,对具体参数进行了设计。采用这种定时同步方法的高速解调器进行了原理实验测试,取得了满意的结果,所提出的定时同步方法对高速数据传输方案设计提供了参考。

关键词:定时同步;锁相环;高速传输;DDS

引言

在数字通信系统中,定时同步是接收机必须完成的一个重要工作,定时同步的好坏直接影响到数字接收机的性能。高速数据传输对定时同步提出了新要求,同步算法结构必须简单有效以降低器件速度限制。

定时同步通常采用3种基本方式实现:模拟方式、数字方式和混合方式。鉴于模拟电路所固有的稳定性差、一致性差等问题,模拟方式目前已经很少使用。数字方式采用一个独立于发送端的时钟对接收信号进行直接采样,然后通过插值运算得到信号在最佳判决时刻的近似值。数字方式对采样率要求较高,通常要求采样率是符号速率4倍以上,对ADC有较高的要求。混合方式通过提取接收信号中的时钟误差信息来调整ADC采样时钟,实现定时同步时钟恢复。混合方式具备数字方式结构可靠、成本低、处理灵活等优点,同时降低了对ADC的要求,采样率只需要2倍符号速率,是高速定时同步的较好选择。

所提出的高速定时同步方法采用了混合方式。ADC的采样时钟由DDS产生,DDS相当于锁相环中的VCO。锁相环的鉴相器、环路滤波是全数字的,在FPGA内实现。定时同步是通过锁相环闭环调整实现的。

1 定时同步数字锁相环路设计

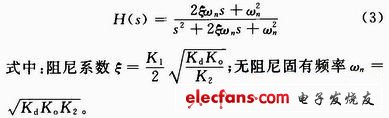

定时同步环路采用理想二阶锁相环。锁相环由鉴相器、环路滤波器、压控振荡器(VCO)组成。理想二阶环的鉴相器增益表示为Kd。环路滤波器传递函数为:

F(s)=K1+K2/s (1)

式中:K1为环路滤波器比例通路的增益系数;K2为环路滤波器积分通路的增益系数。

压控振荡器的传递函数为:

V(s)=Ko/s (2)

式中Ko为VCO的增益。

由式(1),式(2)可得到理想二阶环的传递函数:

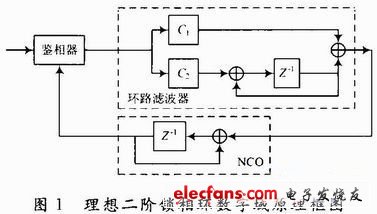

根据脉冲响应不变法,由式(3)可得到理想二阶锁相环的数字域原理框图如图1所示。

图1中环路滤波器的两个参数C1,C2计算式为:

式中:ts为采样周期。

阻尼系数为固定值通常取ζ=0.707,无阻尼固有频率ωn的取值根据锁相环频率捕获范围确定,可取为与要求捕获频率相近的值。由式(4)计算出C1和C2即完成理想二阶数字锁相环的参数设计。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)