摘要:设计了一组基于CPLD的PLC背板总线协议接口芯片,协议芯片可以区分PLC的背板总线的周期性数据和非周期性数据。详细介绍了通过Verilog HDL语言设计状态机、协议帧控制器、FIFO控制器的过程,25MHz下背板总线工作稳定的试验结果验证了协议芯片设计的可行性。

1 背板总线工作原理

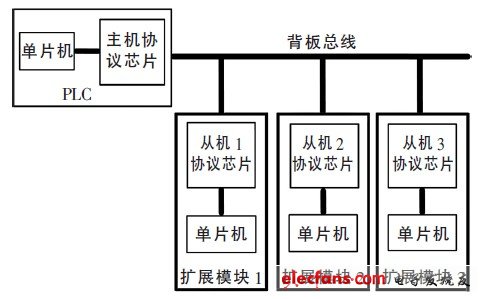

如图1 所示,基于背板总线的数据通信流程如下:

(1)PLC 主机的命令通过主机协议芯片发送到背板总线;(2)从机协议芯片把接收到的命令给扩展模块的单片机, 某一个扩展模块的单片机做出应答,通过从机协议芯片把应答数据送往背板总线;(3)主机协议芯片收到应答数据,并送往PLC主机的单片机。

图1 背板总线通信框图

PLC 主机发往背板总线的数据可以分成两类:一类是I/O 刷新数据,具有周期性,数据交换非常频繁;另一类是诊断性数据,具有非周期性,出现机会较少。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)