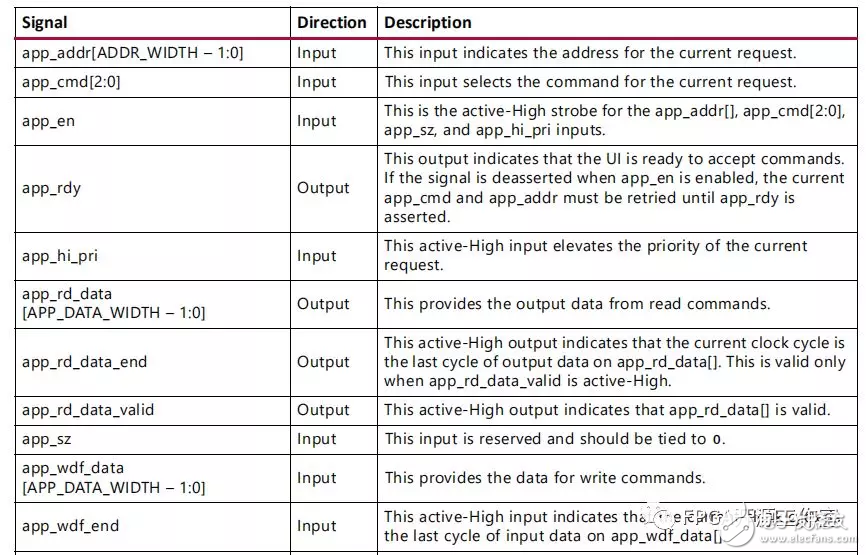

1 mig接口说明

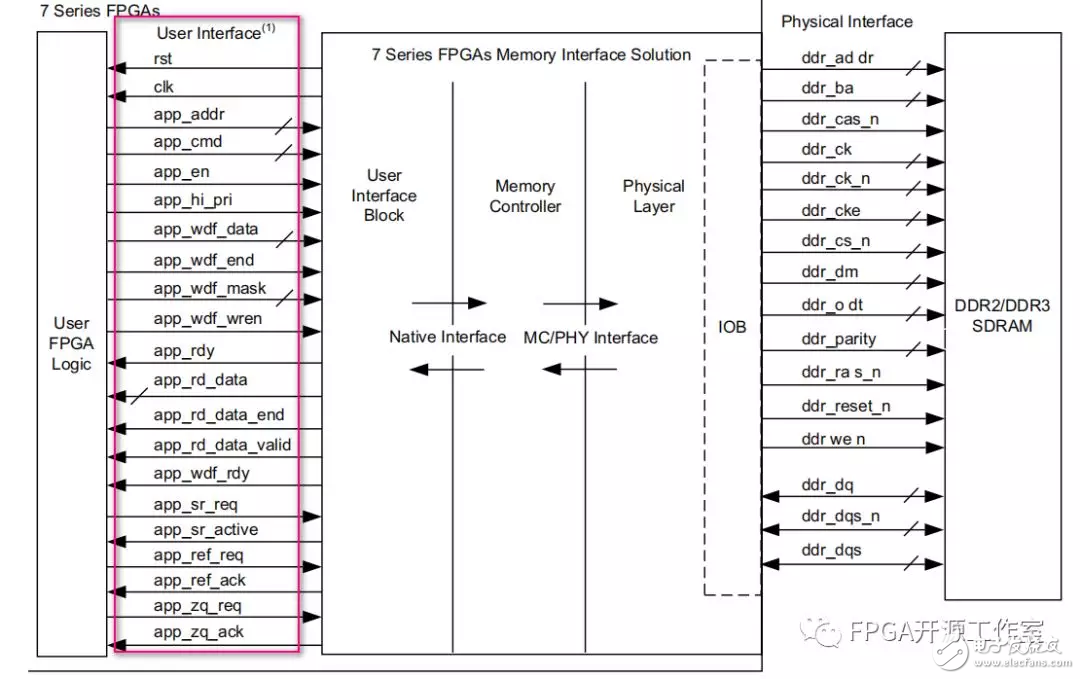

对于mig与DDR3/DDR2 SDRAM的读写时序我们不需要了解太多,交给mig就可以了。我们需要做的是控制好User Interface,写出正确的User logic。想要写好Userlogic,我们就必须清楚每一个用户控制接口的含义:

a. app_addr[ADDR_WIDTH – 1:0]:此输入指示当前提交给UI的请求的地址。 UI聚合外部SDRAM的所有地址字段,并为您提供平面地址空间(Rank,bank,row,colum)。

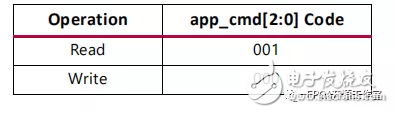

b. app_cmd[2:0]:此输入指定当前提交给UI的请求的命令。

c. app_en:此输入在请求中变化。您必须将所需的值应用于app_addr []和app_cmd [2:0],然后断言app_en以将请求提交给UI。这会通过断言app_rdy来启动UI确认的握手。

d. app_wdf_data[APP_DATA_WIDTH – 1:0]:该总线提供当前正在写入外部存储器的数据。

e. app_wdf_end:此输入指示当前周期中app_wdf_data []总线上的数据是当前请求的最后一个数据。

f. app_wdf_wren:此输入表示app_wdf_data []总线上的数据有效。

g. app_wdf_rdy:此输出表示写数据FIFO已准备好接收数据。当app_wdf_rdy和app_wdf_wren都被声明时,接受写入数据。

h. app_wdf_mask[APP_MASK_WIDTH – 1:0]:该总线指示app_wdf_data []的哪些字节写入外部存储器以及哪些字节保持其当前状态。通过将值1设置为app_wdf_mask中的相应位来屏蔽字节。例如,如果应用程序数据宽度为256,则掩码宽度取值为32. app_wdf_data的最低有效字节[7:0]使用app_wdf_mask的Bit [0]屏蔽,app_wdf_data的最高有效字节[255:248]使用app_wdf_mask的Bit [31]屏蔽。因此,如果必须屏蔽最后一个DWORD,即app_wdf_data的字节0,1,2和3,则app_wdf_mask应设置为32‘h0000_000F。

i. app_rdy:此输出指示您是否接受当前提交给UI的请求。如果在确认app_en后UI未声明此信号,则必须重试当前请求。如果出现以下情况,则不会声明app_rdy输出:

1》PHY /内存初始化尚未完成;

2》所有bank都被占用(可以看作命令缓冲区已满);

3》请求读取并且读取缓冲区已满;

4》请求写入,没有可用的写缓冲区指针;

5》正在插入定期读取。

j. app_rd_data[APP_DATA_WIDTH – 1:0]:此输出包含从外部存储器读取的数据。

k. app_rd_data_end:此输出表示当前周期中app_rd_data []总线上的数据是当前请求的最后一个数据。

l. app_rd_data_valid:此输出表明app_rd_data []总线上的数据有效。

m. ui_clk_sync_rst:reset信号来自于UI,与ui_clk同步。

n. ui_clk:这是UI的输出时钟。它必须是输出到外部SDRAM的时钟频率的一半或四分之一,这取决于在GUI中选择的2:1或4:1模式。

o. init_calib_complete:校准完成后,PHY将init_calib_complete置‘1’。在将命令发送到内存控制器之前,应用程序无需等待init_calib_complete。

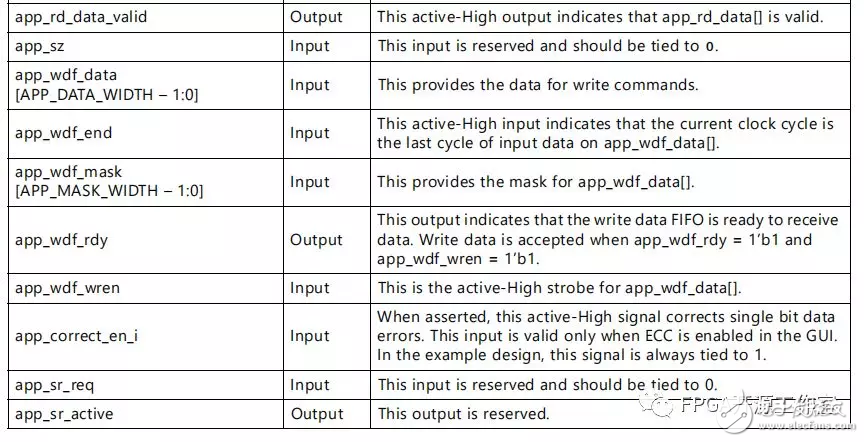

p. app_ref_req:置位时,此高电平有效输入请求内存控制器向DRAM发送刷新命令。它必须在一个周期内进行脉冲以发出请求,直到app_ref_ack信号被置位以确认请求并指示它已被发送,然后置为无效。

q. app_ref_ack:置位时,此高电平有效输入确认刷新请求,并指示该命令已从存储器控制器发送到PHY。

r. app_zq_req:置位时,此高电平有效输入请求存储器控制器向DRAM发送ZQ校准命令。它必须在一个周期内进行脉冲以发出请求,直到app_zq_ack信号被置位以确认请求并指示它已被发送,然后取消置位。

s. app_zq_ack:置位时,此高电平有效输入确认ZQ校准请求,并指示该命令已从存储器控制器发送到PHY。

了解了每个信号的作用我们来讲解mig 用户逻辑的读写时序。

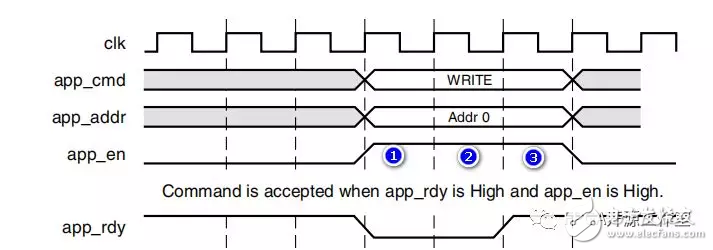

2 命令与地址

如上图所示①,②,③情况,只有在③时刻app_en和app_rdy同时为高电平app_cmd(命令)和(app_addr)地址才有效,所以当需要app_cmd,app_addr有效时app_en必须保持到app_rdy为高电平才有效。

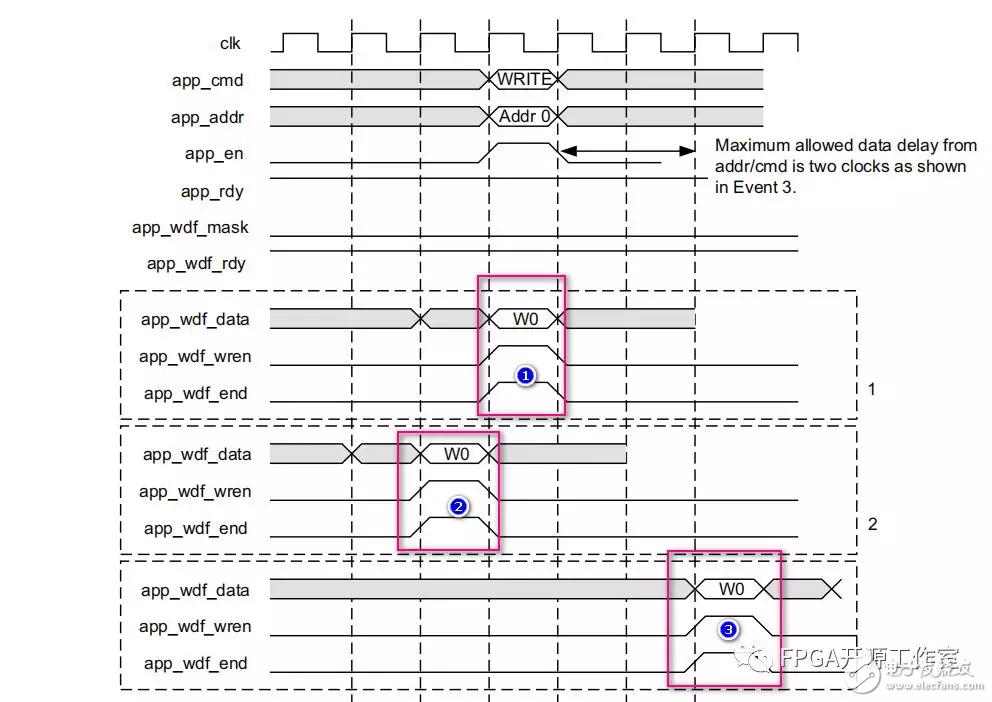

3写时序

如上图所示①,②,③种情况,写命令和写数据直接存在三种逻辑关系。

1,①表示写命令(app_cmd),写当前地址(app_addr)和写数据(app_wdf_data)以及写控制信号(app_en,app_rdy,app_wdf_rdy,app_wdf_wren,app_wdf_end)同时有效。

2,②表示写数据(app_wdf_data)和写控制信号(app_wdf_wren,app_wdf_end)先于写命令(app_cmd)和写当前地址(app_addr)以及其他写控制信号(app_en,app_rdy,app_wdf_rdy)一个用户时钟(ui_clk)。

3,③表示写数据(app_wdf_data)和写控制信号(app_wdf_wren,app_wdf_end)迟于写命令(app_cmd)和写当前地址(app_addr)以及其他写控制信号(app_en,app_rdy,app_wdf_rdy)。最多两个用户时钟(ui_clk)。

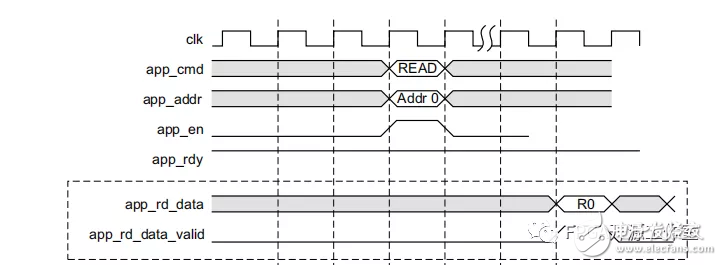

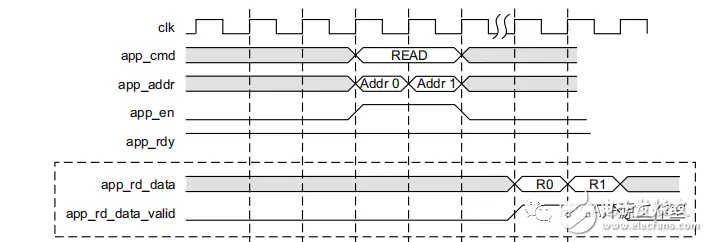

4读时序

如上图所示,当读命令(app_cmd)和当前读地址(app_addr)以及读控制信号(app_en,app_rdy)同时有效时,等待读数据有效信号(app_rd_data_valid)有效时读数据(app_rd_data)有效。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)