引言

为了满足智能卡和可信计算应用需求,设计实现了一款专用SoC芯片。该芯片由微处理器、程序和数据存储器及管理模块、安全逻辑模块、密码服务模块、辅助功能模块、I/0接口组成,能为各种安全应用提供机密性、完整性和身份认证等多种密码服务,以及数据存储、访问控制、安全计算等应用。

专用SoC芯片的安全控制架构设计,首先应对芯片的应用环境进行分析,得到芯片的威胁模型与部署模型,即芯片的潜在攻击者和可能的攻击方式,以及芯片的生产、运输、研发和使用等环节存在的风险问题;其次是根据芯片安全要求与功能规范,通过软硬件协同设计方式,设置相关硬件逻辑、状态寄存器和参数存储区,并实现相关安全策略的软件控制流程;最后对所设计的系统进行安全性分析、仿真验证与FPGA测试。

1 芯片系统安全体系结构设计

基于芯片系统的生产与应用实际,根据受保护资产对芯片安全性影响重要程度和信息技术安全性*估准则,芯片的受保护资产可设计为如下3种安全级别。

0级资产:O层代码的完整性与可信性,0层数据(LEVEL0)的机密性、完整性和可信性,以及芯片各模块功能正确性。0级资产是芯片系统的安全基础,对任一项的保护失败均将导致整个芯片系统拒绝提供任何服务。

1级资产:1层代码的完整性与可信性,1层数据(LEVEL1)的机密性、完整性和可信性。1级资产是系统运行的核心控制态和2级资产的安全基础,对1级资产的保护失败将禁止本层代码及2层代码的执行。

2级资产:2层代码完整性与可信性,2层数据(LEVEL2)的机密性、完整性和可信性。2级资产是芯片系统最上层的受保护资产,对本级资产的保护失败会导致本层代码被禁止运行。2级资产在芯片系统中可以同时存在多个,但每一时刻只有1个投入运行。

1.1 芯片系统安全状态设计

芯片加电运行后,通过执行一系列的命令,获得不同的安全权限,从而也处于某一特定的安全状态。

ST1:出厂初始状态。在信任制造商前提下,芯片在出厂初始状态是可以信赖的。初始状态是芯片的可信基。

ST2:芯片使能状态。首次加电时,上电自检及传输安全认证通过后,芯片所处的状态。芯片在验证各功能模块正确,且。层代码、数据完整性校验通过后,接收传输过程安全认证命令,并利用开发商与制造商的共享秘密,在允许的认证次数范围内对芯片进行真实性认证。

ST3:芯片激活状态。处于使能状态下的芯片,允许开发商通过用户创建命令完成用户创建。在这一过程中,芯片对开发商身份的合法性认证依赖于传输安全认证时的共享秘密。用户创建完成后,置位芯片激活状态标识与所有权获得标识。再次启动时,对开发商的身份合法性认证依赖于输入的共享秘密,以及开发商创建的用户密钥。

ST4:1层代码下载允许状态。为满足芯片使用灵活性的要求,芯片的1层代码可由开发商进行配置。代码下载需对下载命令的发起者进行身份认证,在允许认证次数范围内,若身份认证正确,则置位1层代码下载允许标识,芯片进入1层代码(芯片 *** 作系统)下载允许状态。

ST5:1层代码下载完成状态。在下载控制程序的控制下,完成1层代码下载。下载完成后,下载控制程序调用SHA1模块,对1层代码进行完整性度量与存储,并与输入的下载代码完整性信息进行比较。若完整性验证正确,则置位1层代码使能标识位。

ST6:1层代码运行状态。芯片系统可以由ST3和ST5转入1层代码运行状态。在进入此状态前,需判断1层代码使能标识是否有效,并在验证1层代码及数据完整性正确后进入代码运行状态,执行相应程序完成预定功能。

ST7:2层代码(用户应用程序)下载允许状态。2层代码的下载与调用均在1层代码监控下完成。在1层代码运行状态下,若用户输入2层代码下载命令,1层代码首先认证代码下载命令发起者身份。在允许的认证次数范围内,若身份认证正确,则置位本层敏感信息存储器中的2层代码下载允许标识位,芯片进入2层代码下载允许状态。

ST8:2层代码下载完成状态。与1层代码的下载过程相同,通过调用下载控制程序,完成2层代码的下载。下载完成后,1层代码对2层代码进行完整性度量与存储,对比验证输入的完整性信息。若完整性验证正确,置位LEVEL1中的2层代码使能标识位。

ST9:2层代码运行状态。当2层代码和数据完整性验证正确后,芯片系统可以由ST6和ST8转入2层代码运行状态。当2层代码使能标识有效时,芯片系统可以在ST6或ST8下,通过层次跳转指令,进入2层代码运行状态。在ST6状态下,芯片系统还可通过调用2层代码来完成其相应运算与控制功能。与层次跳转进入ST9不同的是,通过调用2层代码来完成其相应功能时,在2层代码执行完毕后,芯片系统可以返回到ST6。而通过层次跳转命令进入 ST9时,完成规定的功能后,芯片系统保持在ST9,或者通过系统复位返回ST3,不允许其返回ST6。

1.2 状态位与控制参数设置

为实现上述各状态之间的正常跳转,芯片系统需要设置相应的状态位与控制参数,以寄存芯片运行时的控制信息和工作状态。状态位与控制参数设置是芯片安全体系结构建立的基础,基于芯片的权限状态划分,参照TPM与ATMELSC系列安全芯片对状态位与控制参数的配置,将LEVEL0作为专用SoC芯片状态位与控制参数的存储区,其具体设置如表1所列。

表1 LEVEL0状态位与控制参数配置表

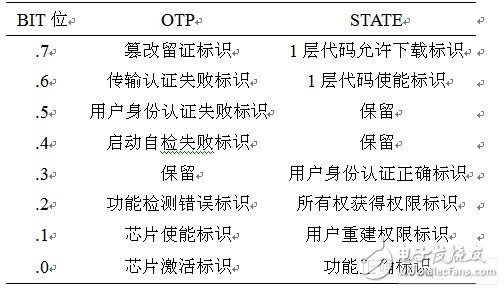

在表1中,OTP(One TIme Programmer)区是一次性编程区,用于芯片一次性设置的权限标识与状态留证。STATE为系统状态标识,用于标识芯片当前的权限状态信息。OTP 与STATE中各位的作用与位的对应关系如表2所示,其中各位均为高电平有效。

表2 OTP与STATE中状态位功能表

M_AUTH为制造商与开发商的共享秘密,M_PUBKEY为制造商公钥,SN为产品序列号,它们共同用于芯片的传输过程安全认证。 EK(Endors- ement Key)为芯片系统的身份认证密钥对,在实际应用过程中,芯片通过调用EK私钥对数据进行签名,以表明自身的合法身份。AIK(Attes-taTIon IdenTIty Key)为开发商身份认证密钥对,在用户身份创建过程中由片内随机数与RSA算法IP核生成,用于用户的身份认证。PCR(Pla-tform. ConfiguraTIon Register)是平台配置完整性寄存区。为满足专用SoC芯片在进行FPGA测试时对芯片系统的硬件规模限制,暂时为芯片系统配置了8个PCR,每个 PCR寄存器为20个字节。除PCR6和PCR7外,其余各PCR寄存器存储信息的表达式如下所示。

PCR0 = SHA1(DOWNLOAD)

PCR1 = SHA1(LEVEL0)

PCR2 = SHA1(COS)

PCR3 = SHA1(APPLI)

PCR4 = SHA1(LEVEL1)

PCR5 = SHA1(LEVEL2)

DIR(Data Integrity Register)是芯片系统的数据完整性寄存器,寄存芯片内部数据与代码的完整性信息,具体设计时,为芯片系统配置了3个DIR,分别存储三个层次的数据与代码的完整性,各DIR寄存器存储信息的表达式如下。

DIR0 = SHA1(PCR0||PCR1)

DIR1 = SHA1(DIR1||PCR2||PCR4)

DIR2 = SHA1(DIR1||DIR2||PCR3||PCR5)

USER_AUTH为用户与芯片系统的共享认证秘密,在用户创建时通过相应命令输入,完成用户的身份合法性验证。ERROR_SIG为认证错误次数寄存器,用于芯片系统对字典攻击的防护。ATTACK_EVI是攻击留证寄存器,对芯片系统所遭受的物理攻击次数与方式进行寄存。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)