0 引 言

经过近几年的快速发展,嵌入式系统(Embedded System)已经成为电子信息产业中最具增长力的一个分支。随着手机、PDA,GPS、机顶盒等新兴产品的大量应用,嵌入式系统的市场正在以每年30%的速度递增(IDC预测),嵌入式系统的设计也成为软硬件工程师越来越关心的话题。

在嵌入式系统设计中,低功耗设计(Low Power Design)是许多设计人员必须面对的问题。其原因在于嵌入式系统被广泛应用于便携式和移动性较强的产品中,而这些产品不是一直都有充足的电源供应,往往是靠电池来供电的;而且大多数嵌入式设备都有体积和质量的约束。另外,系统部件产生的热量和功耗成比例,为解决散热问题而采取的冷却措施进一步增加了系统的功耗。为了得到最好的结果,降低系统的功耗具有下面的优点:

(1)电池驱动的需要。在强调绿色环保时期,许多电子产品都采用电池供电。对于电池供电系统,延长电池寿命,降低用户更换电池的周期,提高系统性能与降低系统开销,甚至能起到保护环境的作用。

(2)安全的需要。在现场总线领域,本安问题是一个重要话题。例如FF的本安设备,理论上每个网段可以容纳32个设备,而实际应用中考虑到目前的功耗水平,每个网段安装10个比较合适。因此降低系统功耗是实现本安要求的一个重要途径。

(3)解决电磁干扰。系统功耗越低,电磁辐射能量越小,对其他设备造成的干扰也越小。如果所有的电子产品都能设计成低功耗,那么电磁兼容性设计会变得容易。

(4)节能的需要。特别是对电池供电系统,功耗与电压的平方成正比即:P=V2/fC+PstaTIc,因此节能更为重要。

1 功耗产生的原因

1.1 集成电路的功耗

目前的集成电路工艺主要有TTL和CMOS两大类,无论哪种工艺。只要电路中有电流通过。就会产生功耗。通常,集成电路的功耗主要有4个:

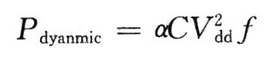

(1)开关功耗。对电路中的电容充放电而形成,其表达式为:

式中:Vdd为电源电压;C为被充放电的电容:α为活动因子;f为开关频率。

(2)静态功耗和动态功耗。当电路的状态没有进行翻转(保持高电平或低电平)时,电路的功耗属于静态功耗,其大小等于电路电压与流过电流的乘积;动态功耗是电路翻转时产生的功耗,由于电路翻转时存在跳变沿,在电路翻转瞬间,电流比较大。存在较大的动态功耗。目前大多数电路都采用CMOS工艺,静态功耗很小,可以忽略。起主要作用的是动态功耗,因此从降低动态功耗人手来降低功耗。

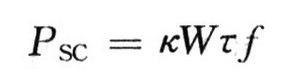

(3)短路功耗。因开关时由电源到地形成的通路造成的,其表达式为:

式中:κ由工艺和电压决定;W为晶体管宽度;τ为输入信号上升/下降的时间;f为工作频率。

(4)漏电功耗。由亚阈值电流和反向偏压电流造成。目前大多数电路都采用CMOS工艺。故漏电功耗很小,可以忽略。

1.2 电阻的功耗和有源器件的功耗

通常为负载器件和寄生元件产生的功耗。有源开关器件在状态转换时,电流和电压比较大,将引起功率消耗。另外,CMOS电路中最大的功耗来自于内部和外部的电容充放电产生的功耗。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)