随着NI的FPGA产品的广泛使用,很多同事和客户都碰到了一些FPGA编程时遇到的问题。由于FPGA不能实时调试,每次修改一点代码之后都要编译很长时间之后才能看到修改的效果,所以,我们希望尽量在FPGA编写代码时就将更多的问题考虑到位。本文针对项目过程中碰到的一些实际问题进行阐述,希望可以为大家在FPGA编程过程中提供一些帮助。

项目描述:该项目是一个实时频谱监测、流盘以及跳频信号检测的需求。具体参数是IQ速率为100MHz,流盘5分钟(要做类似Reference Trigger的效果,即按下按钮之前的一分钟和按下按钮之后的四分钟信号一起流盘),检测跳频信号的时间点和相应的频点,其中跳频信号的参数是:突发性,每次持续1ms~20ms,跳频信号在每个频点上的持续时间是1us~20us,跳频频率70000/s,每个频点上的信号带宽是5MHz;使用的硬件是5792+7966.其中与FPGA相关的部分就是数据采集和跳频信号的检测。对于数据采集部分,5792有专门的采集范例可以供大家参考,而跳频信号的检测算法是将数据每隔128个点做一次FFT(100M的采样率,对于1us的跳频信号持续时间,对应为100个时域采样点)。做出的FFT结果如果超过阈值,则将FFT结果的序号回传给上位机进行保存。

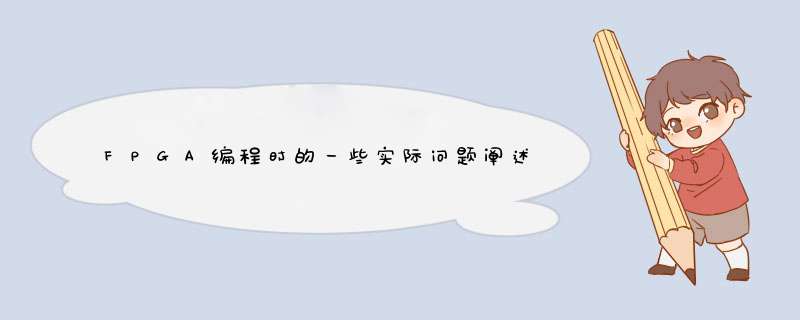

解答: 一、DMA传输的速率对于PXIe-7966R,官网上标定的DMA的传输速率为800MB/s,理论上可以完全满足项目中的400MB/s的传输速率要求。但实际测试过程中,传输的速率接近但总是达不到400MB,这直接影响了信号的实时采集和流盘。经了解,FPGA的DMA BenchMark与FIFO的数据位宽、总线带宽以及DMA控制器的速率都有一定关系。见下图:

注:上图中PXIe系统下,FPGA的时钟使用的是200MHz的时钟。而PXI系统下,FPGA的时钟使用的是160M (U8 和U16),133M(U32和U64)。

注:上图中使用的机箱是PXIe-1075,使用的控制器是PXIe-8130.

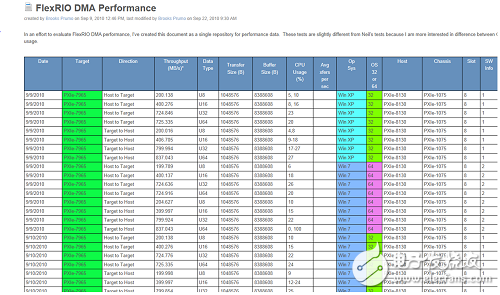

通过观察上述PXIe和PXI板卡的速率统计,可以看到:

对于PXI板卡,在 U8场景下,FPGA每秒钟产生160MB的数据,U16场景下FPGA每秒产生320MB的数据。众所周知,PCI总线的传输带宽为133MB/s,那为什么上图中U8情况下的速率才33MB/s,U16情况下的速率才66MB/s呢?这是因为PCI总线的传输模式是并行传输,总线位宽和时钟频谱分别是32位和33M(一般的desktop都是这样的配置),也就是说每个时钟周期传输32个比特的数据。因此,如果传输的是U8或者U16的数据类型,那么相当于每个传输周期浪费了3/4或者1/2的位宽。因此,U8情况下每次只能传输一个字节,结合33MHz的时钟频率,使得DMA 的Benchmark只有33MB/s。U16的情况下的DMA速率为66M也是可以理解的。而U32以及U64的情况下,只能达到133M的极限速率。

对于PXIe板卡,FPGA读写 FIFO的时钟固定为200MHz,因此,如果FIFO的数据类型是U8,那么每秒钟FPGA端就产生200MB的数据;如果FIFO的数据类型是U16,那么每秒钟FPGA端就产生400MB的数据量。这些数据量远小于1075机箱的单槽带宽(PCIe Gen 1 ×4,1GB/s),因此,总的DMA Benchmark 就等于FPGA端产生数据的速率。如果FIFO的数据类型为U32,那么FPGA产生数据的速率就达到了800MB,这几乎1075机箱的单槽传输极限,因此U32场景下DMA的BenchMark接近800MB/s。继续增加FPGA端FIFO的位宽,在200MHz的时钟频率下FPGA每秒钟产生1.6GB的数据,但这时PCIe总线的传输速率不可能再大幅提升,因此,U64情况下DMA的Benchmark 还是在800MB左右,所以我们很容易得出DMA的传输速率限制为总线的单槽传输带宽。

实测1085+8135环境下的DMA速率

为了验证此种情况(U64,200M时钟)下DMA的传输速率限制确实为总线的单槽传输带宽,我们有理由假设,如果使用1085机箱(单槽传输速率为4GB/s),DMA的传输速率应该可以达到1.6GB/s。因此,我又搭建了相关的系统对1085机箱下的7966 DMA速率进行测试:

硬件环境:PXIe-8135+PXIe-1085+PXIe-7966

测试方法:在7966中以200M的时钟不断将U64数据写入到FIFO中,FIFO大小2048;上位机中对FIFO进行全速读取(缓冲区中有多少点读多少点),上位机缓冲区设置为200M;

测试结果:DMA速率900MB/s左右.修改上位机中FIFO的缓冲区大小,DMA速率没有出现大的波动,依然在900MB/s。观察CPU占用率在18~20%,每次循环查看缓冲区中的点数10000点不到,说明上位机的读取速率完全不是瓶颈。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)