SOPC(SystemOnProgrammableChip) 是用可编程逻辑技术把整个系统放到一片硅片上的一种特殊嵌入式系统一方面,它片上系统(SOC)完成整个系统的逻辑功能;另一方面,它是可编程系统,具有灵活的设计方式,可裁剪,扩充,升级,并具备软硬件在系统可编程功能J.S)PC 是PID 和ASIC 技术融合的结果,可以认为SOPC代表了半导体产业未来的发展方向。本文采用EDA 软件QuartuslI 中的SOPCBuilder 构建了一个SOPC 系统。并以构建的系统为平台进行电子钟的软件设计:最后在Altera公司FPGA 多媒体开发平台DE2 上进行实现该方案不同于基于处理器或控制器及SOC 的嵌入式系统,基于SOPC 的嵌入式系统具有可配置的特点,不会包括任何专用外设,而是可根据需要灵活地在一片FPGA 中构造外设接口。

电子钟是一种用数字电子技术实现时、分、秒自然计时的装置,与机械式时钟相比具有更高的准确性和直观性,而且使用寿命较长,与机械钟相比具有更高的准确性和直观性,具有更长的使用寿命,已得到广泛的使用。数字钟的设计方法有许多种,例如可用中小规模集成电路组成电子钟,也可以利用专用的电子钟芯片配以显示电路及其所需要的外围电路组成电子钟,还可以利用单片机来实现电子钟等等。这些方法都各有其特点,其中利用单片机实现的电子钟具有编程灵活,以便于功能的扩展。

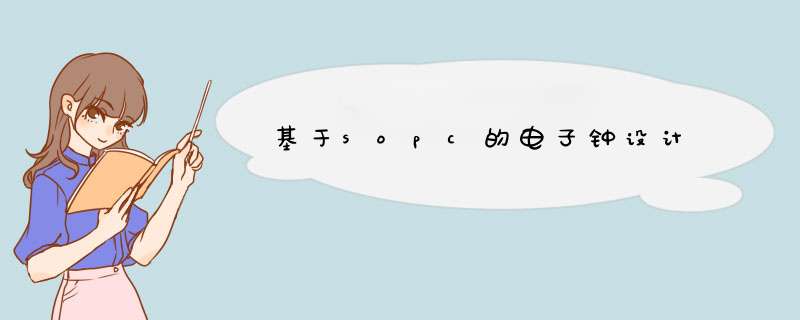

电子钟设计原理数字钟的示意如下图所示。它由石英晶体振荡器、分频器、计数器、译码器显示器和校时电路组成。振荡器产生稳定的高频脉冲信号,作为数字钟的时间基准,然后经过分频器输出标准秒脉冲。秒计数器满60后向分计数器进位,分计数器满60后向小时计数器进位,小时计数器按照“24翻1”规律计数。计数器的输出分别经译码器送显示器显示。计时出现误差时,可以用校时电路校时、校分。

1) 具有正确的时、分、秒计时功能。

2) 计时结果要用数码管分别显示进、分、秒的十位和个位。

3) 有校时功能。当S键按下时,分计数器以秒脉冲的速度递增,并按60min循环,即

计数到期59min后再回到00。当工A键按下时,时计数器以秒脉冲的速度递增,并按24h循环,即计数到23h后再回00。

4) 利用扬声器整点报时。当计时到达59分59秒时开始报时,在59分50秒、52秒、54秒、56秒、58秒时鸣叫,鸣叫声频为500hz;到达59分60秒时为最后一声整点报时,频率为1khz。

控定时器的基本组成数字钟钟控定时器由:计数器、D触发器、数据选择器、数据分配器、译码器、报时器、闹时器组、分频器和一个或非门这九大模块构成。计数器主要分为24进制计数器和60进制计数器,24进制计数器对数字钟的小时位计行计数,60进制对数字钟的分和秒进行计数。D触发器主要是用在对数字进行校准时的按键消抖作用,以免在校时的时候产生抖动信号。数据分配器的作用是在动态译码时选择输出数据。译码器对输出信号进行译码在数码管上显示出来,让大家数字钟的表示直观。报时电路是使时钟在整点有报时功能而设计的。闹时器是对时钟进行比较产生闹时电信号的电路。

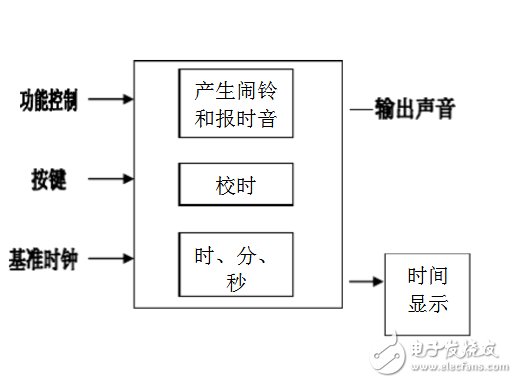

D触发器的设计在本设计中运用到了3个D触发器,它主要是用在对数字进行校准时的按键消抖作用,以免在校时的时候产生抖动信号。

在电路中用到了D触发器74LS74,74LS74的管脚图如图3-1。

触发器,它是由门电路构成的逻辑电路,它的输出具有两个稳定的物理状态(高电平和低电平),所以它能记忆一位二进制代码。触发器是存放在二进制信息的最基本的单元。按其功能可为基本RS触发器触、JK触发器、D触发器和T触发器。

这几种触发器都有集成电路产品。其中应用最广泛的当数JK触发器和D触发器。不过,深刻理解RS触发器对全面掌握触发器的工作方式或动作特点是至关重要的。事实上,JK触发器和D触发器是RS触发器的改进型,其中JK触发器保留了两个数据输入端,而D触发器只保留了一个数据输入端。D触发器有边沿D触发器和高电平D触发器。74LS74为一个电平D触发器。

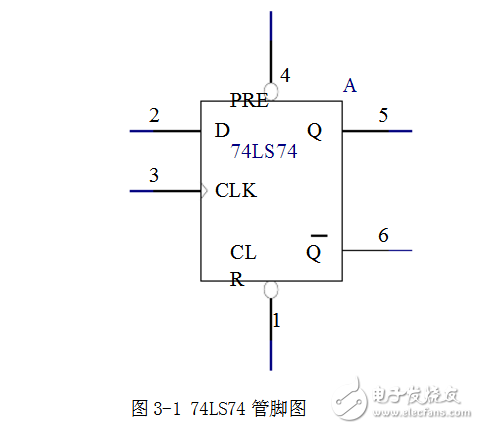

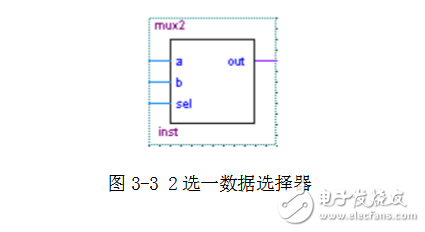

数据选择器的设计在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器,也称多路选择器或多路开关。数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号。

通过QuartusII软件进行编译后,仿真结果如图3-2所示,

打包后成元器件如图3-3所示;

计数器是一种计算输入脉冲的时序逻辑网络,被计数的输入信号就是时序网络的时钟脉冲,它不仅可以计数而且还可以用来完成其他特定的逻辑功能,如测量、定时控制、数字运算等等。

数字钟的计数电路是用两个六十进制计数电路和“24进制”计数电路实现的。数字钟的计数电路的设计可以用反馈清零法。当计数器正常计数时,反馈门不起作用,只有当进位脉冲到来时,反馈信号将计数电路清零,实现相应模的循环计数。以六十进制为例,当计数器从00,01,02,……,59计数时,反馈门不起作用,只有当第60个秒脉冲到来时,反馈信号随即将计数电路清零,实现模为60的循环计数。

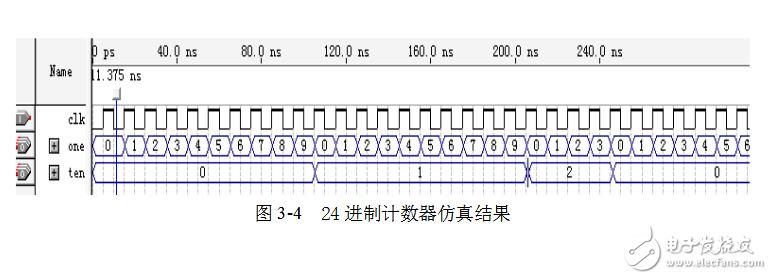

下面是用Verilog HDL语言编写的24进制、60进制计数器的程序代码: 1)24进制计数器程序代码;

module count24(ten,one,clk); output[3:0] ten,one; input clk;

reg[3:0] ten,one; always @(posedge clk) begin

if(ten[3:0]==2&&one[3:0]==3) begin

ten[3:0]《=0; one[3:0]《=0; end

else if(one[3:0]==9) begin

one[3:0]《=0;

ten[3:0]《=ten[3:0]+1; end else

one[3:0]《=one[3:0]+1; end

endmodule

通过QuartusII软件进行编译后,仿真结果如图3-4所示,

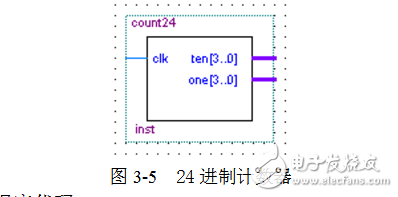

打包后成元器件如图3-5所示;

module count60(cout,ten,one,clk); output[3:0] ten,one; output cout; input clk;

reg[3:0] ten,one; always @(posedge clk) begin

if(one[3:0]==9) begin

one[3:0]《=0; if(ten[3:0]==5) ten[3:0]《=0; else

ten[3:0]《=ten[3:0]+1; end else

one[3:0]《=one[3:0]+1; end

assign cout=(ten[3:0]==0&&one[3:0]==0)?1:0; endmodule

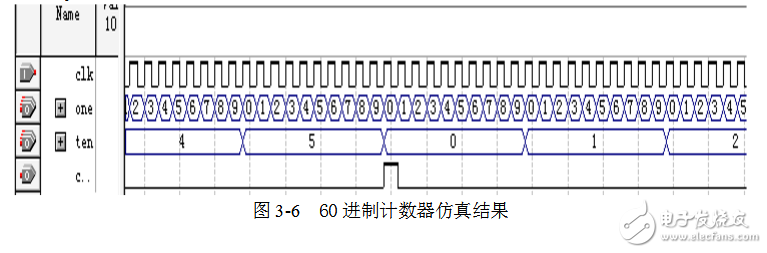

通过QuartusII软件进行编译后,仿真结果如图3-6所示;

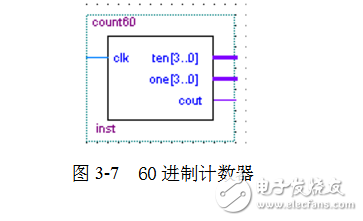

打包后成元器件如图3-7所示

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)