摘 要:介绍一种基于PCI总线的高效链式DMA控制器的设计与实现,用于高速宽带的计算机外设接口。利用Altera公司的PCI核——PCI_MT32搭建基于此控制器的数据采集平台,并成功应用在DVB数据接收卡中。

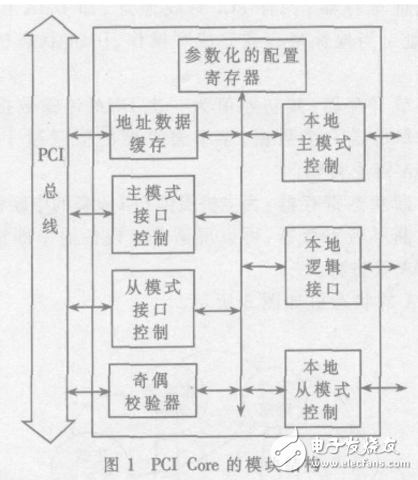

1991年PCISIG(外围部件互连专业组)成立,提出了PCI的概念Altera公司提供的软件包:PCICompiler可以参数化地生成用于PCI接口的IP核——Megacore。该IP核包含了PCI控制电路的所有功能,完成总线协议的转换,并将复杂的、电气和时序要求高的PCI转换为易于 *** 作的本地接口逻辑。用户可以基于其生成的IP核模块,设计自己的外部设备接口逻辑。Altera的MegaCore包括四种类型:PCI_MT64、PCI_MT32、PCI_T64和PCI_T32。它们都具有灵活的通用接口,遵循PCI协议2.2版,严格的工业级验证和多款优化FPGA。考虑通常的PC主板都支持32位PCI,而且DMA控制器必须工作在主模式下,因此选择了PCI_MT32,其模块结构如图1所示。

·参数化的配置寄存器:保存PCI设备的基本信息,可以通过软件参数设定寄存器。

·地址数据缓存:缓存PCI总线上的地址数据。

·主模式接口控制模块控制模块:在主模式下对PCI总线的 *** 作。

·从模式接口控制模块:在从模式下对PCI总线的 *** 作。

·奇偶校验器:当校验出错时,生成一个报错信号输出到配置寄存器。

·本地主模式控制模块:主模式下,控制本地逻辑的接口。

·本地从模式控制模块:从模式下,控制本地逻辑的接口。

·本地逻辑接口模块:控制本地端接口的地址、数据、控制、字节使能等。

1DMA控制器针对高带宽、低延时和大数据量的多媒体数据,设计了基于PCIcore的DMA数字卫星电视接收卡。DVB协议中的基本数据单元为192字节,因此把一次DMA传输的数据包定为192字节。

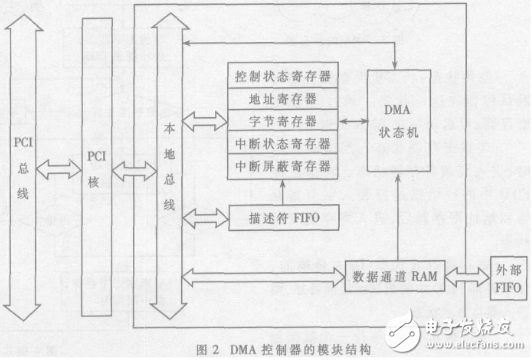

1.1DMA控制器的结构DMA控制器由DMA寄存器、描述符描述符FIFO、DMA状态机、数据通道RAM四个模块构成,如图2所示。

DMA寄存器是主机控制DMA的窗口,包括控制状态寄存器状态寄存器、地址寄存器、字节寄存器、中断状态寄存器和中断屏蔽寄存器。描述符FIFO是一个32×256的FIFO,在链式DMA模式下可以暂存128组DMA的描述符。DMA状态机是控制PCI总线数据传输的核心,主模式下的DMA有主模式写和主模式读两种类型。主模式写是把数据通道RAM里的数据包通过PCI总线传送到从设备,主模式读则读取从设备的数据包传送到数据通道RAM中。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)