SK海力士DRAM产品规划担当 柳成洙

SK海力士IPM规划 Technical Leader 李圣学

在上一篇发表于《电子工程专辑》的文章1中,SK海力士DRAM产品规划担当柳成洙和SK海力士IPM规划Technical Leader李圣学介绍了HBM3如何满足市场对DRAM和内存产品的更高需求。两位作者再次合作,通过本文介绍他们的团队在SK海力士未来计划中所发挥的作用。

尽管业界对包括摩尔定律、内存墙差异等传统原则的有效性争议不断,但半导体领域仍普遍认为,多年来内存行业的价值主张在很大程度上始终以系统级需求为导向,已经突破了系统性能的当前极限。基于对先进技术和解决方案开展的研究,内存行业在未知领域进行了更深入的探索,并致力于实现“全球首创”和“全球最佳”创新成果,让整个IT行业从中受益。

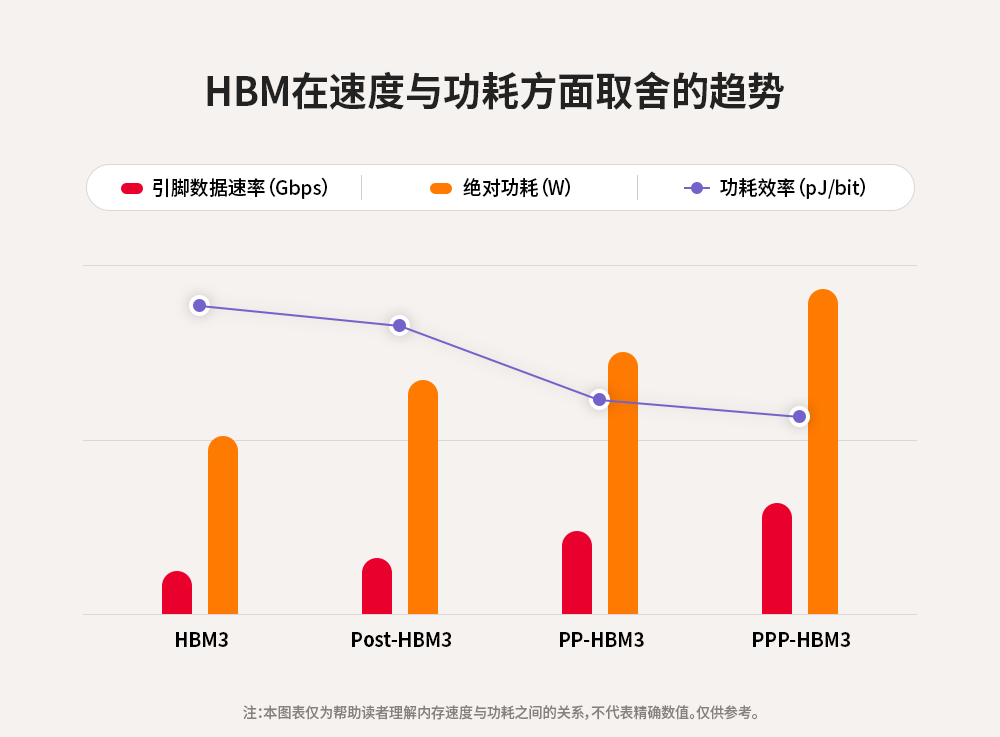

然而,很明显的一点是,内存性能(通常为内存带宽)提升将出现拐点,因为越来越多人质疑是否能一直通过内存级的取舍(如功耗、散热、占板空间等)来提高系统性能。这一问题在HBM领域最为明显,HBM处于系统和内存性能层级的顶端,是包括超级计算机、高性能计算、自动驾驶和机器学习等下一代应用无可争议的技术推动因素。虽然内存供应商坚持认为,为了确保所需的有效带宽性能,一定的功耗、散热、占板空间是不可避免的,但片上系统(SoC)行业的支持者却认为,考虑到固定的系统级预算,应将取舍影响保持在最低水平。

图1. HBM在速度与功耗方面取舍的趋势

这种针锋相对的观点迫使双方争相发挥自身行业领导力,率先设定开创性内存规划和技术里程碑,成为内存领域发展的风向标,并推动行业从传统的演进路线转为定义全新内存结构和标准的非常规方式,以开发突破性解决方案。目前,SK海力士已成为HBM领域无可争议的领导者,近年来逐步推出多款HBM产品,其中包括分别于2019年和2021年开发全球首创的HBM2E和HBM3,以及新近宣布向英伟达(NVIDIA)供货HBM3。

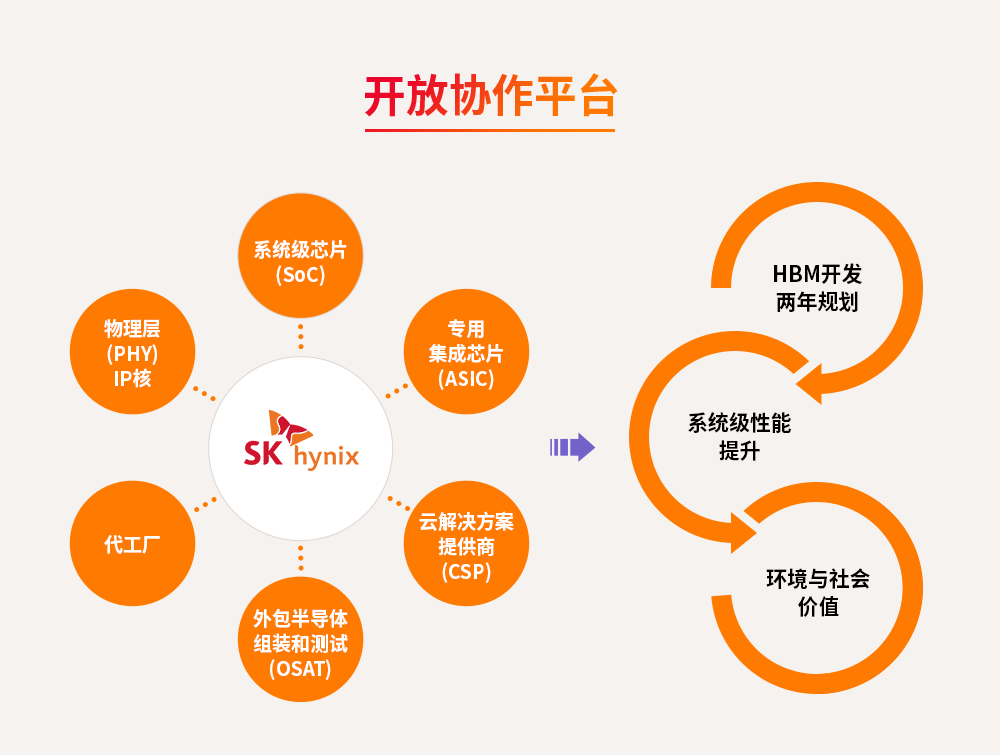

在这方面,业界期待SK海力士DRAM产品规划担当率先构建行业协作和合作伙伴关系,确保在全球最快且性能最佳的HBM系列产品的支持下,未来高带宽内存规划交付成果能够满足全球客户和合作伙伴的需求。SK海力士DRAM产品规划担当响应这一行业呼声,为推动HBM生态系统设定了大约每两年推出一款全新HBM系列产品的产品路线图。SK海力士相信,暂定的HBM开发两年规划将非常有助于确保系统层面的进步,以及依托最具附加价值的应用以突破现有性能极限。

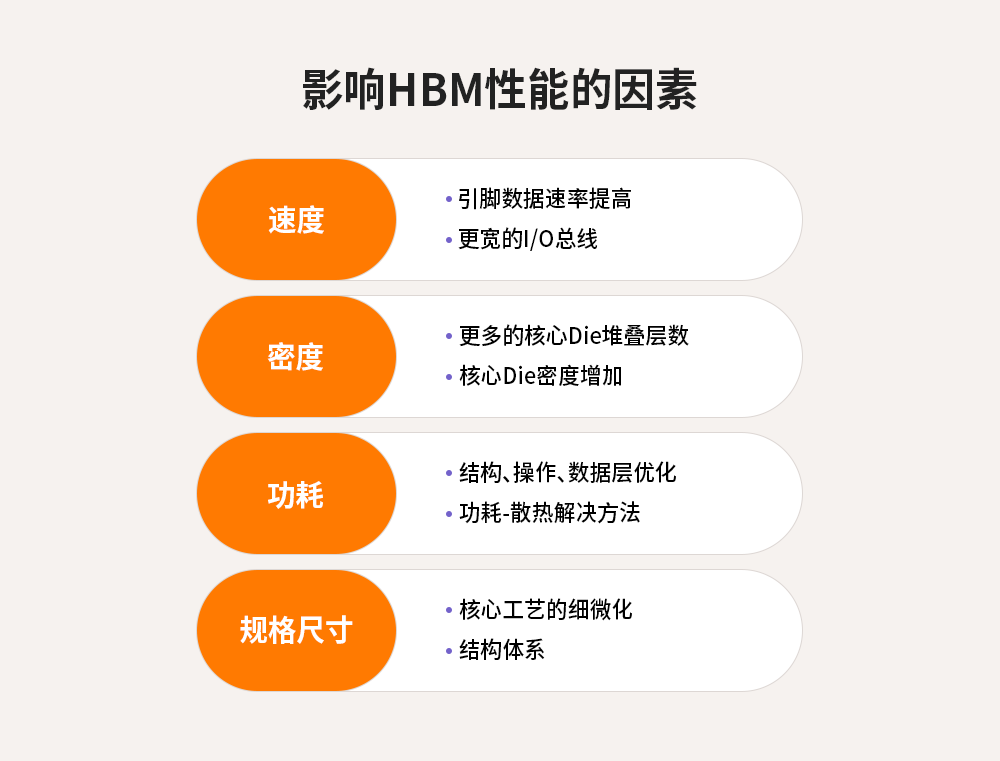

为了保持这一长期规划策略和技术进步,SK海力士DRAM产品规划正加强内外部努力,以突破目前HBM在速度、密度、功耗、占板空间等方面的极限。首先,为了打破速度极限,SK海力士正在评估提高引脚数据速率的传统方法的利弊,以及超过1024个数据的I/O总线位宽,以实现更好的数据并行性和向后设计兼容性;换言之,即用最少的取舍获得更高的带宽性能。针对更大数据集、训练工作负载所需的更高内存密度要求,SK海力士开始着手研究扩展Die堆叠层数和物理堆叠高度,以及增加核心Die密度以优化堆叠密度。

SK海力士也在致力于提高功耗效率(pJ/bit),通过评估从最低微结构级别到最高Die堆叠概念的内存结构和 *** 作方案,最大限度地降低每带宽扩展的绝对功耗。SK海力士深知,由于现有中介层光罩尺寸的物理限制以及支持处理单元和HBM Cube的其他相关技术,实现总内存Die尺寸最小化尤为重要,因此SK海力士努力在不扩大现有物理尺寸的情况下增加存储单元数量和功能,从而实现整体性能的飞跃。完成上述任务的前提是:SK海力士要与生态系统合作伙伴携手合作和开放协同,将HBM的使用范围从现有系统扩展到潜在的下一代应用。

图2. 影响HBM性能的因素

目前围绕相关话题的争论仍在继续,包括最终的最优性能目标是什么;如何开发突破性解决方案以满足所有相关方需求;什么是合适的折中方案等等。这些讨论无可避免并且需要解决,这样才能实现HBM开发两年规划。

与相关方紧密合作和保持沟通以产生不懈的推动力,使其在未来规划策略和技术进步层面发挥能量,对此SK海力士DRAM产品规划担当有深刻了解,因此,SK海力士DRAM产品规划担当正在与SoC(系统级芯片)、ASIC(专用集成芯片)、CSP(云解决方案提供商)、OSAT(外包半导体组装和测试)、代工厂、物理层(PHY)/IP核等领域的主要厂商开展紧密合作,合力解决现有技术问题,同时创造全新价值以推动半导体行业发展,并作为一家负责任的技术公司,不断创造环境和社会价值。

图3. SK海力士的HBM开放协作平台愿景

编辑:黄飞

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)