【导读】输入/输出缓冲器信息规范(IBIS)是一种行为模型,作为生成器件模型的标准格式而在全球受到欢迎。器件模型的精度取决于行业提供的IBIS模型的质量。因此,为信号完整性仿真提供高质量、可靠的IBIS模型是对客户的坚定承诺。

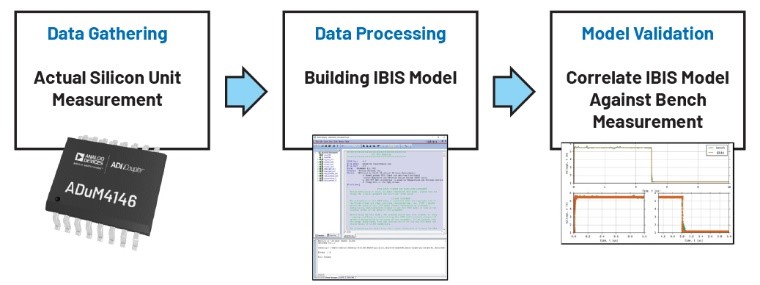

生成IBIS模型的一种方法是通过仿真,但在某些情况下,设计文件不可用,因而无法从仿真结果生成IBIS模型。在这种情况下,通过基准测量生成IBIS模型是解决这一问题的方法,它能提供高质量和更真实的器件行为模型。图1显示了通过基准测量生成IBIS模型的完整过程。使用实际芯片,提取器件的接收器和驱动器缓冲器行为以表示电流与电压(I-V)数据和电压与时间(V-t)数据。

图1.通过基准测量生成IBIS模型的过程

然后使用实际试验台设置在完整负载条件下验证模型。此程序提供质量等级2b的IBIS模型。为了实现更高质量等级(3级)的模型,生成的IBIS模型还将针对器件的晶体管级设计进行验证,同样采用推荐的负载条件。

为了表征质量,IBIS质量任务组制定了一种包含五个QC(质量控制)阶段的质量控制流程。表1为定义不同质量等级的清单。

表1.IBIS质量规范中的质量等级

表1中列出的质量等级提供了IBIS模型质量标准,该标准因供应商而异。制定IBIS模型精度标准将能确保客户获得准确可靠的模型。模型的质量等级越高,其数据就越准确,因为更高的质量等级需要更多的验证。

根据《半导体建模:用于信号、电源和电磁完整性仿真》一书(Roy Leventhal和Lynne Green撰写),IBIS正确性检查清单有5个公认的质量等级。

质量等级0—通过IBISCHK

质量等级0要求至少应通过IBIS解析器检查。IBISCHK必须产生零错误;如果无法消除所有警告,则必须对其进行解释。理想情况下,不应有任何警告,但人们认识到,有些警告是无法消除的。解析器检查产生的“错误”、“警告”和“注意”消息可作为IBIS模型制作商识别错误并轻松纠正错误的指南。IBIS模型解析器检查参见图2。

图2.IBIS模型通过IBISCHK

质量等级1—达到检查清单文件中规定的完整性和正确性

质量等级1的IBIS模型不仅要通过质量等级0检查,还要通过基本仿真测试的正确性和完整性检查。封装寄生参数、引脚配置和负载参数应正确定义。斜坡速率和典型值/最小值/最大值必须符合器件规格。另外,可以参考这里列出的质量等级1下的详细要求。

质量等级2a—与仿真相关

质量等级2a将IBIS模型的性能与器件的晶体管级设计进行比较。连接到负载时的IBIS模型性能与相同负载下器件的晶体管级设计进行相关处理。然后比较两个仿真设置的结果,并检查模型是否达到了质量等级2a。细节将在“验证和结果”部分讨论。

质量等级2b—与实际芯片测量相关

质量等级2b将IBIS模型的性能与器件的实际单元进行比较。与质量等级2a一样,在相关期间必须将相同的负载连接到两个设置。根据相关结果判断模型是否达到质量等级2b。细节将在“验证和结果”部分讨论。

质量等级3—晶体管级仿真与IBIS基准测量的相关

质量等级3要求根据晶体管级设计和实际单元验证IBIS模型。要使模型达到质量等级3,它必须通过质量等级2a和2b的相关性检查。此外,模型必须通过IBIS解析器测试(质量等级0),并通过IBIS质量检查清单的检查(质量等级1)。细节将在“验证和结果”部分讨论。

应用案例

本文研究的案例是ADuM4146,它是一款专门为驱动碳化硅(SiC) MOSFET而优化的隔离式栅极驱动器。ADuM4146有三个输入引脚(VIP、VIN和RESET)和两个开漏引脚(READY和FAULT),但本文针对每种缓冲器类型仅讨论一个引脚。这是因为,对于缓冲器类型相似的引脚,构建和验证IBIS模型的过程是相同的。VIP引脚将作为输入缓冲器的用例,FAULT将作为开漏缓冲器的用例。

需要注意的是,尽管相似的缓冲器类型具有相同的IBIS建模和验证过程,但这并不一定意味着它们具有相同的IBIS数据。本文对每种缓冲器类型仅讨论一个引脚,以简化对IBIS模型构建和验证过程的解释。

ADuM4146采用标准小型宽体封装(SOIC_W),封装在验证过程中以寄生电阻、电感和电容(RLC)的形式表示。封装工程师通过仿真提取封装RLC值。专用印刷电路板(PCB)与封装寄生的情况类似,也是由寄生RLC表示,其值由PCB工程师提取。

图3.ADuM4146功能框图

表2显示了ADuM4146引脚配置和每个引脚对应的缓冲器类型。此信息将用于IBIS模型的[Pin]关键字。

表2.ADuM4146引脚排列及其对应的缓冲器类型

IBIS基准测量步骤

通过基准测量收集数据可能会受到不同外部因素的影响。应补偿这些因素以满足相关并提供高质量模型。

为了最大限度地减少外部因素的影响,待测器件(DUT)放置在专用夹具上,以减小可能导致被测器件行为不准确的干扰电容,如图4所示。寄生电容是实际硅片测量中的一个重要问题,并且常常是限制器件模型工作频率和带宽的因素。

图4.IBIS基准测量专用夹具

通过基准测量生成IBIS模型的步骤:

准备设置

表3显示了基准测量的IBIS预建模阶段要求,表4显示了定义缓冲器行为的不同模型类型和模型组成。模型类型在文章“IBIS建模—— 第1部分: 为何IBIS建模对设计成功至关重要”和“IBIS 建模——第2部分: 为何以及如何创建您自己的IBIS模型”中有详细讨论。您也可以参考IBIS建模手册。

表3.IBIS基准测量建模前阶段

表4.IBIS基准测量缓冲器类型选择

试验台设置

了解器件的运行方式对于IBIS模型的数据收集至关重要。如图1所示,这是第一阶段,通过提取I-V数据和V-t数据来完成。两者都以表格形式表示。

I-V数据包括ESD箝位行为和驱动器强度,而V-t数据表示从低/高电平状态到高/低电平状态的转换。切换行为是通过将负载连接到输出引脚来测量,这个负载与输出缓冲器将要驱动的值相等。然而,通常的负载值为50Ω,代表典型的传输线阻抗。

对于I-V测量,使用能够吸收和提供电流的可编程电源和曲线跟踪器来扫描电压并收集缓冲器的电流行为。建议在–VDD至2×VDD的电压范围内以及典型值、最小值和最大值拐角处获取数据。V-t测量需要使用具有适当带宽和低电容探头的示波器。

DUT安装在专用工具上,使用温度强制系统在不同温度条件下进行测试,以获取最小、典型和最大性能。在这种情况下,最小(最弱驱动强度、最慢边沿)数据是在125°C下获取,最大(最强驱动强度、最快边沿)数据是在–40°C下获取。

基准数据提取

一旦验证试验台设置已准备就绪,就可以开始收集所需I-V和V-t数据的过程。输出和I/O缓冲器需要I-V表和上升/下降数据,而输入缓冲器只需要I-V表。

○ I-V(电流与电压)数据测量

I-V曲线测量涵盖四个IBIS关键字——[Pullup]表示驱动高电平时上拉元件的I-V行为,[Pulldown]表示驱动低电平时下拉元件的I-V行为,而[Power Clamp]和[GND Clamp]表示高阻抗状态下ESD保护二极管的I-V行为。

要测量I-V特性,请将器件安装在专用板上,并将电源和接地引脚连接到电源。准备温度强制系统,调整到所需温度,等待其稳定。在推荐范围内扫描电压,然后使用曲线跟踪器测量所需缓冲器的电流。

用于上拉和电源箝位数据的扫描设备的正节点应连接到电源电压,负节点应连接到引脚,而用于下拉和接地箝位数据的扫描设备以地为参考。当曲线跟踪器无法扫描整个范围时,可能需要外推。

图5显示了输入缓冲器(VI+) I-V接地箝位测量的试验台设置,而图6显示了其测量行为。当输入降低到地以下导致负电流时,接地箝位电路被触发,使电流接近并稳定为零。输入引脚(VIP)没有电源箝位元件,因此其模型不会有电源箝位数据。

图5.用于I-V箝位测量的ADuM4146试验台设置

图6.ADuM4146输入缓冲器试验台测量的接地箝位

对输出缓冲器的ESD箝位、上拉和下拉数据实施相同的方法。但在这种情况下,ADuM4146 READY和FAULT引脚为开漏缓冲器。因此,它们没有上拉元件,只需要下拉数据。

图7.ADuM4146开漏缓冲器下拉结果

图7显示了ADuM4146开漏缓冲器的下拉数据结果。下拉曲线从负电流开始,然后穿过零到达正象限,也在–VDD至2×VDD的范围内。

○ 缓冲电容(C_comp)提取

根据IBIS建模手册(IBIS 4.0版),“每个焊盘的总裸片电容或C_comp参数是从焊盘向缓冲器看到的电容,用于完全布局布线的缓冲器设计,不包括封装效应”。获得C_comp值的一种方法是使用以下公式。

其中:

CIN = 器件输入电容

Cpkg = 器件封装电容

○ V-t(输出电压与时间)数据测量

V-t曲线测量也涵盖了四个IBIS关键字——[Rising Vddref]和[Falling Vddref]与以电源为参考的负载的从低到高和从高到低的转换有关,而[Rising Gndref]和[Falling Gndref]与以地为参考的负载的从低到高和从高到低的转换有关。与这些相关的是关键字[Ramp],它定义了从一种状态变为另一种状态时的转换速率,取波形的20%到80%。

测量上升和下降时间数据需要在驱动所需负载的缓冲器上使用示波器。在这种情况下,使用一个50Ω电阻来表示传输线阻抗。对于开漏型,将负载连接到缓冲器和电源电压以测量切换行为(以VDD1为基准)。务必使用温度强制系统以根据需要稳定温度,从而捕获最小、典型和最大范围。图8显示了ADuM4146 READY和FAULT引脚切换行为的实际试验台设置。ADuM4146数字输出引脚为开漏型,因此只需要以电源电压为基准的上升和下降行为。

图8.ADuM4146 READY/FAULT切换行为的试验台设置

图9和图10显示了在晶体管级仿真和实际芯片测量中捕获的FAULT引脚上升和下降波形。两种设置使用相同的负载条件,即50Ω连接到VDD1,跨越典型值、最小值和最大值拐角。

图9.ADuM4146 FAULT引脚上升波形(以VDD1为基准)

图10.ADuM4146 FAULT引脚下降波形(以VDD1为基准)

构建IBIS模型

创建IBIS模型的下一阶段是处理收集的数据并构建模型本身。在此阶段,在必要的关键字之后以IBIS文本格式插入原始数据表,包括器件参数。详细过程参见文章“IBIS建模—— 第1部分: 为何IBIS建模对设计成功至关重要”。

图11.从基准测量生成的ADuM4146 IBIS模型

图11显示了从基准测量生成的ADuM4146 IBIS模型。该模型应通过IBIS解析器检查,包括基本检查,例如I-V和V-t表之间的匹配以及检查表格数据的单调性。在继续验证过程之前,应完全解决所有错误、警告和注意事项。此外,模型应通过IBIS质量检查清单的检查。

验证和结果

本文的验证过程将遵循本系列的第二篇文章“IBIS建模——第2部分:为何以及如何创建您自己的 IBIS模型”中说明的步骤,其中讨论了有关IBIS模型验证过程的更多详情。

图12.IBIS模型质量等级3验证过程流程图

模型首先必须通过解析器测试,这可以使用集成了IBISCHK的软件来进行检查,或使用来自ibis.org的开源可执行代码进行检查。通过解析器测试后,模型必须与其晶体管级原理图或实际芯片单元相关联。本文旨在实现质量等级为3级的模型,因此ADuM4146的IBIS模型将与其晶体管级原理图和实际单元相关联。设置品质因数(FOM)值以确定IBIS模型是否会通过这两种相关性检查。在这种情况下,两种相关性的FOM值必须大于或等于95%才能通过质量等级3 IBIS模型验证。图12显示了IBIS模型达到质量等级3所必须通过的验证过程的流程图。

曲线度量下方的面积将用于计算两种相关性的FOM值。须将相同的负载条件放置在这两组相关性上。在验证过程中,建议按照数据手册中指示的负载条件来测试设备的正常运行。

为了根据参考正确验证IBIS模型(例如,IBIS与基准测量的相关性),必须把信号在基准测量设置中经过的PCB走线添加到IBIS仿真设置中。

以下是实现质量等级为3级的IBIS模型的两个条件。

IBIS质量等级2a验证

图13.IBIS模型质量等级2a验证过程

图13显示了IBIS模型质量等级2a验证过程。该相关处理旨在评估IBIS模型数据将在何种程度上产生与晶体管级仿真结果相匹配的仿真。图14显示了ADuM4146的输入和开漏缓冲器的IBIS模型仿真设置以及负载条件。

图14.ADuM4146输入和开漏缓冲器仿真设置

图15.ADuM4146晶体管级设计仿真设置和负载条件(输入缓冲器)

图16.ADuM4146晶体管级设计仿真设置和负载条件(开漏缓冲器)

图15和16分别显示了输入和开漏缓冲器的晶体管级设计仿真设置以及负载条件。器件的封装RLC值添加在缓冲器和负载之间,以再现IBIS设置中的封装寄生效应。

图17.晶体管级设计与IBIS模型验证结果的关系(输入缓冲器)

图18.晶体管级设计与IBIS模型验证结果的关系(开漏缓冲器)

图17和图18分别显示了IBIS模型在标准负载下运行并将结果与使用相同负载下的晶体管级参考仿真进行比较时,输入和开漏缓冲器的相关结果。一个50Ω电阻用作开漏缓冲器的IBIS与晶体管级相关性设置的负载。使用10μs脉冲输入对两种设置进行瞬态分析。

表5显示了两个缓冲器模型在与晶体管级原理图相关时计算出的FOM值。两个缓冲器模型的FOM值均大于95%,因此IBIS模型达到了质量等级2a。

表5.输入和开漏缓冲器的质量等级2a验证FOM值

IBIS质量等级2b验证

IBIS质量等级2b要求模型与基准测量相关,因此需要考虑可能影响基准测量性能的因素。执行基准测量的主要挑战是信号衰减,大部分是由走线寄生效应引起的。利用实际单元测量数据时,最好使用带有低电容探头的专用板,以尽可能减少走线寄生效应的影响。在这种情况下,IBIS试验台专用板是信号完整性问题的解决方案,可减少混入目标信号的干扰信号所引起的衰减。图19显示了IBIS质量等级2b的验证过程。

图19.IBIS模型质量等级2b验证过程

IBIS模型相关性的主要目标是获得尽可能接近参考的结果。在示波器中捕捉上升/下降时间数据时,最好使用负载极低的探头,以减少信号衰减。探头和仪器组合引入的误差会对目标信号产生重大影响。根据Tektronix,“使用特殊滤波技术和正确选择工具以去除测量系统对信号的影响、显示边沿时间以及其他信号特性,是测量实际芯片性能时要考虑的关键因素”。

图20和图21分别显示了使用输入和开漏缓冲器并考虑负载条件的IBIS模型的仿真设置。串联到缓冲器的RLC值是来自电路板走线的寄生值。添加负载以复制实验室设置时,重要的是要考虑其对模型性能的影响。

图20.实际IBIS仿真设置和负载条件(输入缓冲器)

图21.实际IBIS仿真设置和负载条件(开漏缓冲器)

图22.试验台设置和负载条件(输入缓冲器)

图23.试验台设置和负载条件(开漏缓冲器)

图22和23分别显示了负载条件下输入和开漏缓冲器的试验台设置的示意图。5V脉冲信号用于驱动连接到50Ω负载的开漏缓冲器。图24和图25分别显示了输入和开漏缓冲器的IBIS仿真与基准测量的相关结果。

图24.实际芯片单元与IBIS模型验证结果的关系(输入缓冲器)

图25.实际芯片单元与IBIS模型验证结果的关系(开漏缓冲器)

表6显示了输入和开漏缓冲器的FOM值与实际芯片基准测量的相关性。FOM值大于95%,这意味着两个缓冲器的IBIS模型达到了质量等级2b。由于该模型通过了质量等级2a和质量等级2b检查,因此现在可以将其视为质量等级3 IBIS模型。

表6.输入和开漏缓冲器的质量等级2b验证FOM值

结论和要点

通过基准测量构建高质量IBIS模型时,提取硬件与模型相关所需的数据是最具挑战性的步骤之一。通过仔细关注细节并了解I/O电路的行为,可以实现实验室测量与IBIS仿真结果的密切相关。在相关处理中,尽可能多地消除衰减是获得高FOM值的关键。考虑到这一点,建议使用专用测试平台以及匹配良好的设备和配件,以确保信号的完整性。

同时须记住,在相关处理中,IBIS模型和试验台设置在信号经过的走线方面必须完全相同。这将能减少相关性引起的误差,从而提高FOM值。

拥有质量等级为3级的IBIS模型对半导体供应商和客户来说都是一个优势,有助于确保模型从硅前验证到实际芯片测量时获得更高的精度水平。

致谢

感谢ADI设计工程师、ADGT测试开发工程师和ISO团队全力支持完成本项目。此外,感谢ADGT系统集成经理对项目赞助的支持。

关于ADI公司

ADI是全球领先的高性能模拟技术公司,致力于解决最艰巨的工程设计挑战。凭借杰出的检测、测量、电源、连接和解译技术,搭建连接现实世界和数字世界的智能化桥梁,从而帮助客户重新认识周围的世界。详情请浏览ADI官网www.analog.com/cn。

关于作者

Christine C. Bernal于2007年6月加入ADI,担任产品工程师。2016年,她在新技术集成团队为各种ADI产品开发IBIS模型。Christine于2015年毕业于马尼拉马普阿大学,主修微电子,获电子与通信工程硕士学位。

Janchris Espinoza是ADI公司新技术集成团队的产品应用工程师。主要负责对ADI产品进行IBIS建模和仿真。他于2019年在ADI的Analog Garage团队实习,并于2020年9月正式加入ADI。他于2020年2月毕业于德拉萨大学,获电子工程学士学位。

Aprille Arjhilynne Hernandez-Loyola于2015年8月加入ADI。她是新技术集成团队的产品应用工程师。她主要从事建模和电路仿真工作,尤其是ADI产品的LTspice®和IBIS。她毕业于德拉萨大学(达斯马里尼亚斯分校),获电子与通信工程学士学位。

作者:ADI产品应用工程师Christine C. Bernal,ADI产品应用工程师Janchris Espinoza,ADI产品应用工程师Aprille Hernandez-Loyola

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

步进电机想要的“凌波微步”全靠它

具有集成电容器的降压稳压器如何帮助降低EMI和节省布板空间

NFC芯片市场空间巨大,如何把握产业向好机会?

为什么电机驱动是工业企业实现“碳中和”的关键技术?

自动化设备的LiDAR与电源管理解决方案

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)