【导读】本文探讨了关断时发生的栅极电压欠冲对导通开关特性的影响。这种影响来自于阈值电压的迟滞效应,指栅偏压变化时,阈值电压的完全可恢复瞬态偏移。阈值电压的迟滞效应是由半导体-绝缘体界面缺陷中,电荷的短期俘获和释放引起的。因此,关断时的栅极电压欠冲会对碳化硅(SiC)MOSFET的开关特性产生影响。

我们在应用条件下,使用双脉冲测量进行研究。研究结果表明,关断栅极电压欠冲对阈值电压迟滞效应的影响与恒定的关断栅极电压相同,进而会对导通开关特性产生影响。然而,似乎只有在违背数据手册所定义的最小瞬态电压的边界条件时,这种影响才有意义。

1 引言

在现代电力电子系统中使用SiC MOSFET,需要电路开发人员处理硅基功率器件闻所未闻的器件特性。阈值电压迟滞效应就是这样的特性之一。文献表明,这种由关断栅极电压所触发的效应,会大大影响SiC MOSFET的开通特性[2][4][9][10] [11]。例如,[2]证明了,虽然跨导不受影响,但导通过程中的阈值电压和米勒电压同时依赖于关断栅极电压。该试验还强调,虽然栅源电荷在导通期间几乎不受关断栅极电压的影响,但当关断栅极电压从-3V降低到-7V时,米勒电荷增加了大约5%。

这一分析在[4]所报告的研究结果中得到了证实。除了[2],我们还可以通过[4]清楚地看出,利用这种效应,有助于降低开通时的能量损耗。关断栅极电压对SiC MOSFET的开通行为有很大影响。与具体使用的器件技术无关,因此必须在设计阶段就考虑到这一点[4]。

为此,从原则上来看,我们之前报告的[2]研究十分简洁明了,并对该效应进行了深入的理论性描述,因此,可以供电路设计人员使用。但是,该分析只讨论了恒定关断栅极电压的影响,并没有涵盖更快的动态变化,例如,栅极电压欠冲。

因此,在本研究中,我们将重点关注,在阈值电压迟滞的背景下,栅极电压欠冲对SiC MOSFET开关特性的影响。

2 实验设置

本研究补充了[2]所报告的研究结果,[2]所讨论的双脉冲测量,是在240Ω的高外部栅极电阻下进行的,从而可以忽略电路中寄生元件的影响。其测量结果可以直接追溯到SiC MOSFET芯片技术的物理特性。然而,由于开关速度低,不能立即得出其与类似应用条件的相关性。

本研究对此进行了补充,我们在典型应用条件下(VDD=800V,ID=20A,T=25℃),使用采用TO247-4封装的1200V SiC MOSFET进行了双脉冲测量(见图2)。

SiC MOSFET的开关特性(特别是在高开关速度下)很大程度上取决于测量电路的寄生元件及其封装。因此,在这项研究中,有必要减少所测电路的寄生影响。否则,这些影响可能会对SiC MOSFET电气行为产生误导性的解释。因此,我们使用了杂散电感为6.5nH的低电感设置。

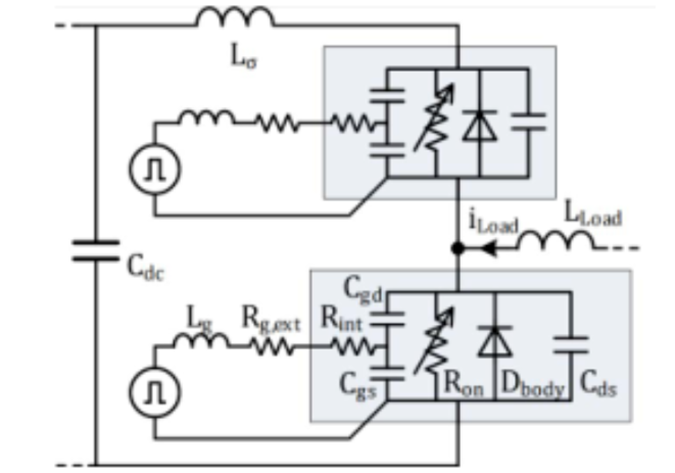

图1为测量设置的等效电路图,图2为测量设置图。

图1:双脉冲设置的等效电路图

与传统的高电感设置相比,这种低电感设置不采用母线轨,而是采用低ESL直流母线陶瓷电容器。

图2:具有可调杂散电感的定制双脉冲设置

如前所述,除了测量电路之外,快速开关SiC MOSFET的开关特性也在很大程度上受到封装的影响。因此,本研究使用了TO247-4引线封装(见图3)。该封装带有一个辅助源极引脚和一根杂散电感约为4.5nH的源极键合线。

图3:采用TO247-4封装的1200V SiC MOSFET

3 结果与讨论

本节的第一部分说明了应用中的栅极电压欠冲的含义和来源;第二部分解释了电路设计人员该如何评估栅极电压欠冲是否会影响SiC-MOSFET的开关特性;在最后一节,探讨了栅极电压欠冲对开关能量损耗以及器件热行为的影响。

3.1 栅极电压特性

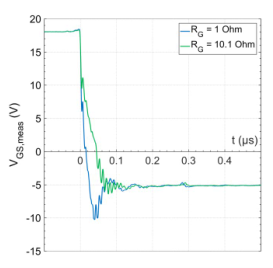

图4清楚地显示了,外部栅极电阻分别为1Ω和10.1Ω时,关断测量脉冲期间,栅极电压随时间的变化。驱动器的关断栅极电压被设为-5V。

图4:关断测量脉冲期间,栅极电压随时间的变化

(T =25°C)

外部栅极电阻为10.1Ω时,被测器件的栅极电压没有明显的欠冲;相比之下,外部栅极电阻为1Ω时,被测器件的最小观测栅极电压约为-10.5V,持续时间为几纳秒。

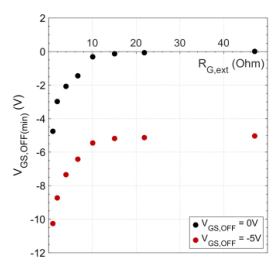

在不同的外部栅极电阻下,重复这些测量,并确定测得的最小关断栅极电压。

图5所示的结果表明,最小栅极电压在很大程度上受到外部栅极电阻的影响,并且栅极电压欠冲可低于静态关断电压5V。

图5:关断测量脉冲期间,栅极电压与RG,ext的关系

这意味着SiC MOSFET被施加的最小关断栅极电压不仅与驱动电压有关,还取决于关断期间栅极电压的额外欠冲。

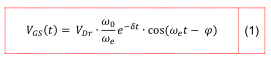

该栅极电压欠冲的幅度可以根据等式(1)计算:

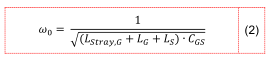

在等式(1)中, 表示栅极环路的谐振频率,具体由等式(2)计算而得:

表示栅极环路的谐振频率,具体由等式(2)计算而得:

在该等式中,LS为辅助源极键合线和引脚的电感,LG为栅极键合线和引脚的电感,LStray为栅极驱动电路的杂散电感。

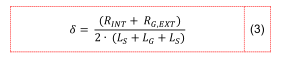

阻尼因子 可以通过内部栅极电阻RINT和外部栅极电阻RG,EXT,按照等式(3)计算:

可以通过内部栅极电阻RINT和外部栅极电阻RG,EXT,按照等式(3)计算:

最后,可以使用等式(5),计算角本征频率 :

:

假设有一个阻尼因子为0的理想的谐振器,则相对栅极电压过冲可以使用等式(6)计算:

该实验的结果表明,在应用中可能会出现栅极电压欠冲。但必须注意,这些栅极电压欠冲是由所使用的SiC MOSFET和栅极驱动电路之间的相互作用造成的,不能只是追溯到所用的SiC MOSFET的电气特性。

然而,如前所述,电路设计人员应确保栅极电压欠冲不超过数据手册所给出的最大瞬态电压限制,并忽略其对导通开关特性的影响。

从理论的角度来看,电荷预计可以在几纳秒内被俘获。利用超快速的测量,数项研究提出了在栅偏压变化的几分之一微秒内,阈值电压的变化[9][10] [11]。这些结果与无辐射多声子模型[12]一致,该模型将电荷俘获描述为,影响阈值电压的、在统计上独立的叠加电荷转移反应。相关的俘获和释放时间常数可以非常低,以至于在欠冲时间内,触发相当大的阈值电压偏移。

因此,预计哪怕是在几纳秒范围内、非常短的关断栅极电压欠冲(见图4),也会由于迟滞效应,导致阈值电压偏移,并可能对开通瞬变产生很大影响。

这种效应鲜为人知,现有文献中也没有关于它的详细描述。因此,我们将在下一节探讨关断期间的栅极电压欠冲是否会影响SiC MOSFET的导通行为。

3.2 开关瞬变

我们在上一节探讨了应用中栅极电压欠冲的含义和来源;并证明了在非常快的开关速度下,可能会出现低于静态关断栅极电压5V的栅极电压欠冲。

本节将介绍和探讨,栅极电压欠冲对后续导通开关特性的影响所产生的结果。

图6显示了栅极关断电压分别为0V和-5V、外部栅极电阻为10.1Ω时,器件的漏极电流和漏极电压随时间的变化。如图4所示,在这个外部栅极电阻下,没有观察到栅极电压欠冲。

图6:漏极电流和漏极电压与时间的关系

(RG,ext=10 Ω)

由于存在迟滞效应,与在0V关断栅极电压下进行的测量相比,在-5V关断驱动电压下,被测器件的阈值电压明显降低。

根据[2][4],在-5V关断驱动电压下,开通瞬态电流应该明显更高。然而,如图6所示,只要驱动电压保持高于-5V,则恒定关断栅极电压的影响就可以忽略不计。

如图4所示,如果缺少适当的栅极电路设计,栅极电压欠冲就可能会明显低于-5V。例如,7Ω的外部栅极电阻和-5V的驱动电压,会导致栅极电压最低达到-7V;而1Ω的外部栅极电阻和-5V的驱动电压,会导致栅极电压最低达到-10.5V。

相应的开关特性见图7和图8。

图7:漏极电流和漏极电压与时间的关系

(RG,ext=7 Ω)

这些导通开关特性表明,在有栅极电压欠冲的两个实验中,关断栅极电压为-5V时,被测器件具有明显更高的漏极电流斜率。在未观察到栅极电压欠冲的测量中,测量结果没有显示出这种差异,这表明额外的关断栅极电压欠冲,会影响导通开关特性。

图8:漏极电流和漏极电压随时间的变化

(RG,ext=1 Ω)

这些结果表明,由观察到的开关瞬态显著增加可知,阈值电压迟滞效应可由栅极电压欠冲触发。

这些结果通过提取开关瞬变得到了进一步的强调。图9显示了相应的漏极电流斜率,图10显示了被测器件在栅极关断电压为0V和-5V时,对应的漏极电压斜率和外部栅极电阻的关系。

考虑到关断栅极电压必须低于-5V,因此,可以认为,在关断栅极电压为0V时进行的测量中,开关瞬态不受滞后效应的影响。相比之下,如图9和图10所示,在关断栅极电压为-5V和外部栅极电阻产生栅极电压欠冲时进行的测量中,开关瞬态速度显著增加。

外部栅极电阻为6.7Ω时,关断栅极电压约为-7V,处于数据手册中给出的最大瞬态栅极电压的范围内。在这种情况下,可以观察到漏极电流斜率从5.5 A/ns增加到6A/ns,漏极电压斜率从53V/ns,增加到60V/ns。

总而言之,这些结果表明,栅极电压欠冲可能会触发阈值电压滞后效应,从而降低阈值电压,并导致更快的导通开关瞬态。但必须注意,这种效应只与漏极电压斜率大于40V/ns的、非常快的开关速度有关。

图9:漏极电流斜率与外部栅极电阻的关系

图10:漏极电压斜率与外部栅极电阻的关系

3.3 开关能量

除了主要与栅极驱动器设计和电磁兼容性问题相关的开关瞬态外,电路设计人员在设计冷却系统时,还必须考虑热损耗。对于这一点,本研究证实了从文献[4]中了解到的情况,即迟滞效应可能会由于更快的开关瞬态,而大大降低导通能量损失。

这种效应见图11。该图显示了,在关断栅极电压分别在0V和-5V时,进行的开关测量中,导通能量损耗与外部栅极电阻的关系。

图11:开通能量损耗与外部栅极电阻的关系

(T= 25°C)

栅极电阻低于7Ω时,与关断栅极电压为0V时进行的测量相比,关断栅极电压在-5V时测得的导通开关能量损耗更低。除非考虑到阈值电压滞后对导通开关特性的影响,否则这一点并不明显,这是因为在通常情况下,导通特性与关断栅极电压无关。

然而,本研究证明了,阈值电压迟滞效应仅在关断栅极电压低于-5V时触发(而非先前报告的-2 V)。研究还表明,即便外部栅极电阻非常低,栅极电压欠冲也仅在-5V范围内。这意味着,关断栅极电压应至少为-2V或更低,才能对导通能量损耗带来明显影响。然而,根据[8,9],如果温度很高,而且关断栅极电压低于-2V,那么SiC MOSFET的高边体二极管内的双极电荷会明显增加。这会导致明显更高的开通能量损耗,从而抵消由于迟滞效应导致的更快开通。

如图12所示,在175°C的结温下,与关断栅极电压为0V时进行的开关测量相比,关断栅极电压为-5V时,被测器件的开通能量损耗要高得多。

图12:导通能量损耗与外部栅极电阻的关系

(T= 175°C)

但这并不意味着迟滞效应不能被用来减少开通能量损耗。但是,为此必须减少SiC MOSFET高边体二极管内的反向恢复电荷(例如,通过缩短死区时间[9]。)

参考文献

[1] P. Sochor, A. Huerner and R. Elpelt, "A Fast and Accurate SiC MOSFET Compact Model for Virtual Prototyping of Power Electronic Circuits," PCIM Europe 2019; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2019, pp. 1-8

[2] A. Huerner, P. Sochor, M. Feil and R. Elpelt, "Influence of the Threshold-Voltage Hysteresis on the Switching Properties of SiC MOSFETs," PCIM Europe digital days 2021; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2021, pp. 1-8

[3] D. Peters, T. Aichinger, T. Basler, G. Rescher, K. Puschkarsky and H. Reisinger, "Investigation of threshold voltage stability of SiC MOSFETs," 2018 PCIM Europe 2022, 10 – 12 May 2022, IEEE 30th International symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, 2018, pp. 40-43, doi: 10.1109/ISPSD.2018.8393597.

[4] Y. Cai et al., "Effect of Threshold Voltage Hysteresis on Switching Characteristics of Silicon Carbide MOSFETs," in IEEE Transactions on Electron Devices, vol. 68, no. 10, pp. 5014-5021, Oct. 2021, doi: 10.1109/TED.2021.3101459.

[5] K. Puschkarsky, T. Grasser, T. Aichinger, W. Gustin and H. Reisinger, "Understanding and modeling transient threshold voltage instabilities in SiC MOSFETs," 2018 IEEE International Reliability Physics Symposium (IRPS), 2018, pp. 3B.5-1-3B.5-10, doi: 10.1109/IRPS.2018.8353560

[6] P. Sochor, A. Huerner and R. Elpelt, "Commutation loop design for optimized switching behavior of CoolSiC (exp TM) MOSFETs using compact models," PCIM Europe digital days 2020; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2020, pp. 1-8.

[7] P. Sochor, A. Huerner, M. Hell and R. Elpelt, "Understanding the Turn-off Behavior of SiC MOSFET Body Diodes in Fast Switching Applications," PCIM Europe digital days 2021; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2021, pp. 1-8.

[8] P. Sochor, A. Huerner, Q. Sun, R. Elpelt, “Understanding the switching behavior of fast SiC MOSFETs”, in PCIM Europe 2022

[9] K. Puschkarsky, H. Reisinger, T. Aichinger, W. Gustin, and T. Grasser, “Threshold voltage hysteresis in SiC MOSFETs and its impact on circuit operation,” in 2017 IEEE International Integrated Reliability Workshop (IIRW), S. Lake Tahoe, California, Oct. 2017.

[10] K. Puschkarsky, H. Reisinger, T. Aichinger, W. Gustin, and T. Grasser, “Understanding BTI in SiC MOSFETs and Its Impact on Circuit Operation,” IEEE Transactions on Device and Materials Reliability, vol. 18, no. 2, pp. 144–153, Jun. 2018, doi: 10.1109/TDMR.2018.2813063.

[11] M. W. Feil et al., “The Impact of Interfacial Charge Trapping on the Reproducibility of Measurements of Silicon Carbide MOSFET Device Parameters,” Crystals, vol. 10, no. 12, Dec. 2020, doi: 10.3390/cryst10121143.

[12] C. Schleich et al., “Physical Modeling of Charge Trapping in 4H-SiC DMOSFET Technologies,” IEEE Trans. Electron Devices, vol. 68, no. 8, pp. 4016–4021, Aug. 2021, doi: 10.1109/TED.2021.3092295.

[13] T. Aichinger, G. Rescher, and G. Pobegen, “Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs,” Microelectronics Reliability, vol. 80, pp. 68–78, 2018, doi: 10.1016/j.microrel.2017.11.020.

来源:Andreas Huerner1, Paul Sochor1, Qing Sun1, Maximilian Feil2, Rudolf Elpelt1

1 英飞凌科技股份公司(德国埃尔朗根)

2 英飞凌科技股份公司(德国纽伦堡)

通讯作者:Andreas Huerner, andreas.huerner@infineon.com

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

打破电动汽车“里程焦虑”,主驱能效如何升级?

如何加强对Type-C数据线的充电保护?

以太网供电实现LED照明应用

自动驾驶汽车的未来趋势:集中式传感器融合

揭秘SMD保险丝:尺寸虽然小,功能不打折,它们是如何做到的?

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)