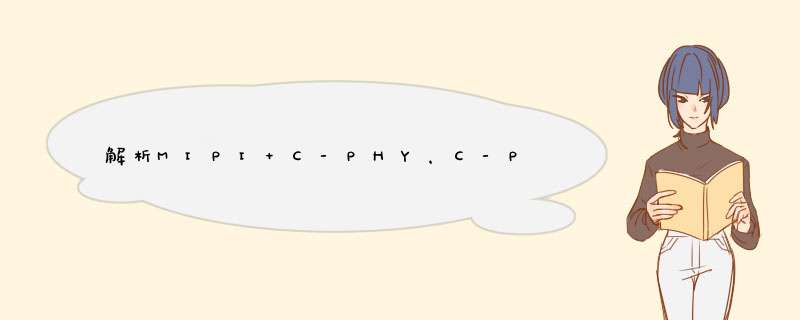

DPHY是源同步系统(有同步时钟通道clock lane),为了提高带宽,CPHY没有同步时钟clock lane,时钟是嵌入到数据中的,当然也涉及到数据编解码。DPHY是1个时钟lane,1/2/4对数据lane,接收端根据时钟边沿采样数据,比如寻找0xb8的同步头。而MIPI CPHY不带时钟lane,必先恢复时钟,然后用恢复时钟采样数据(寻找0xb8的同步头),然后进行数据解码。

CPHY的symbol

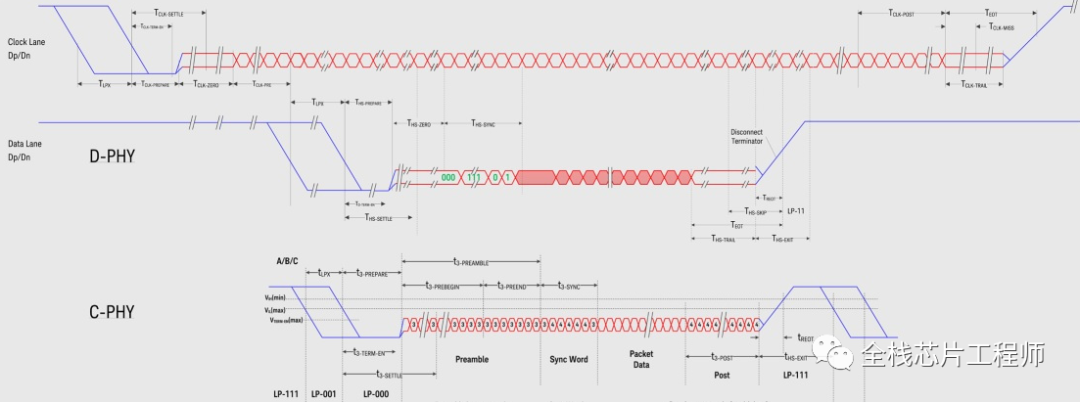

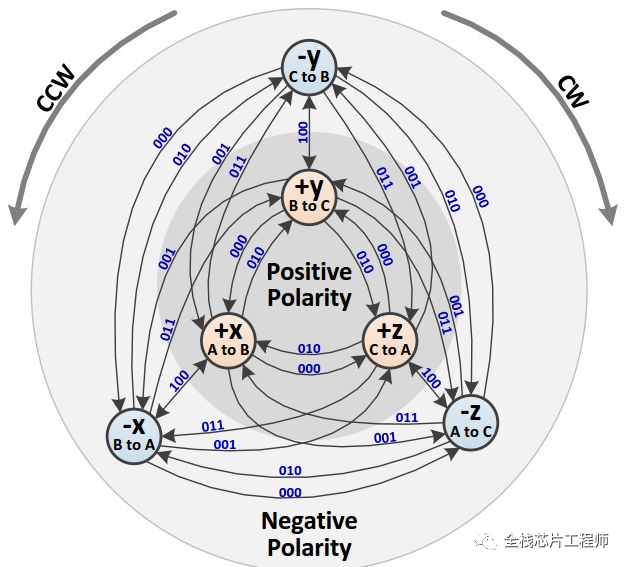

相比DPHY,CPHY没有时钟线;CPHY三线为一lane,三线彼此差分,CPHY最多3lane(即9线)比D-PHY要少一根线。每一根线有三种电平:3/4V,2/4V 和 1/4V,这三个线的电平彼此不同,因此可以有6种排列组合,记为:+x, -x, +y, -y, +z, -z。

请思考一下,为什么没有000、111这两种状态?后面解答。

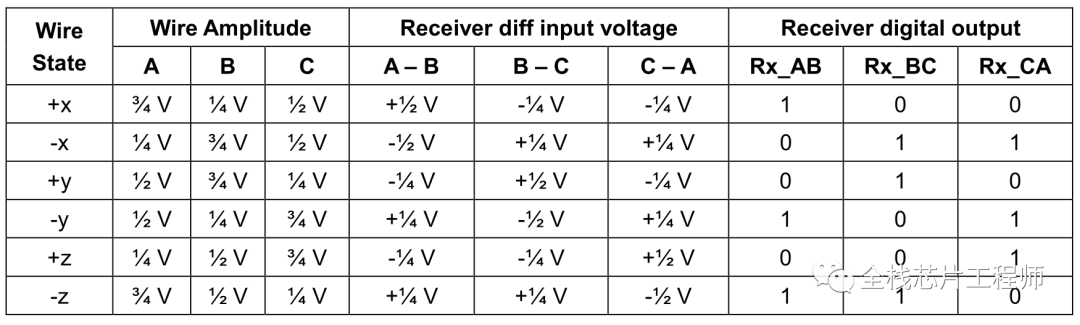

我们对这三个线的电压,两两做差,就可得到下面的眼图。三根线的电压差所形成的形状如同“眼睛”,称之为眼图。每一个Wire status状态切换是一个symbol,每一个symbol代表了3bit 数据,注意,是Wire status的切换才是数据,而非Wire status本身代表数据,读者可以思考下为什么。

C-PHY如何表示传输数据

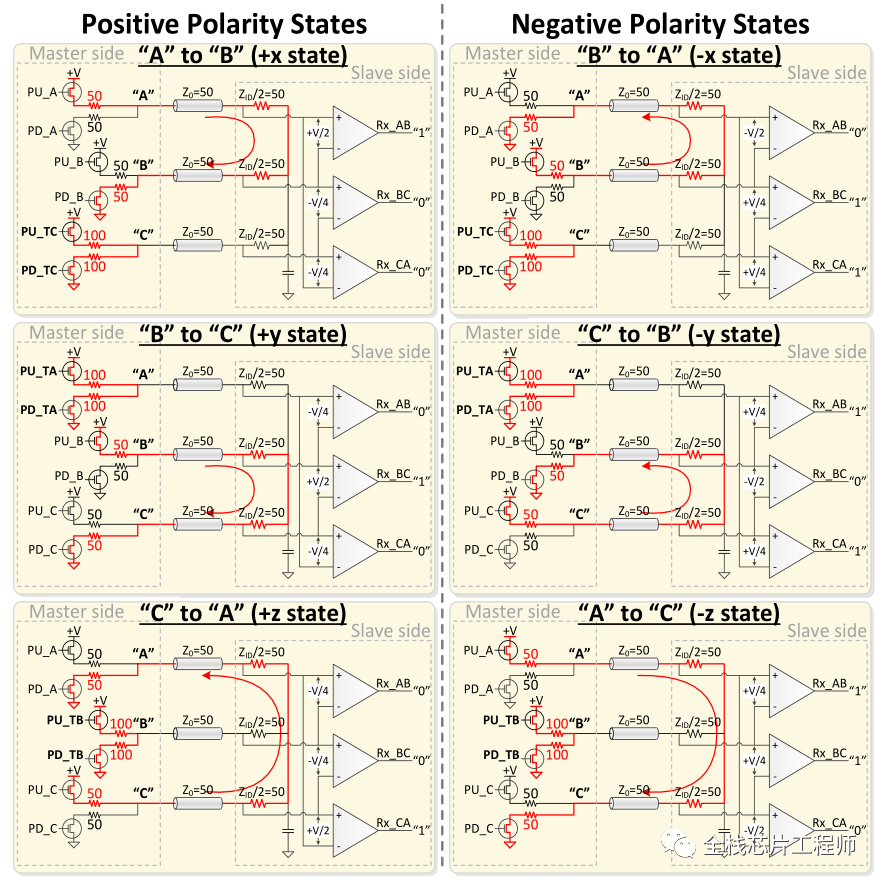

C-PHY是如何表达并传输数据的?就是靠6个状态的切换表示数据的,注意,是Wire status的切换才是数据,而非Wire status本身代表数据,如下图:每一次的状态切换,代表了3bit的数据。

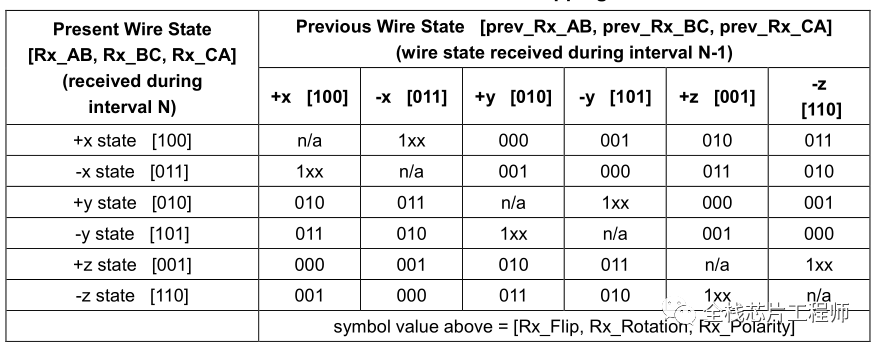

Wire status切换归总为表格:

假设当前状态是+x. 即:

假设要传输的数据000 010 011那么状态的变化是:+x => +z => +x => -y

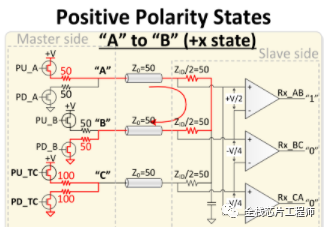

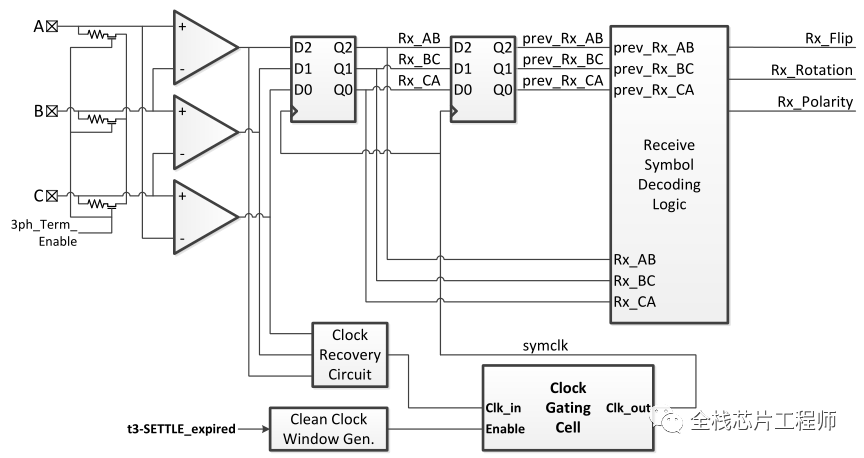

检测symbol状态变化的电路如下图:

CPHY的数据编码

对于D-PHY而言,以Byte为单位进行数据传输。一个UI是1 bit。

对于C-PHY而言,以16bit为单位进行数据传输,一个UI 是16/7 bit。

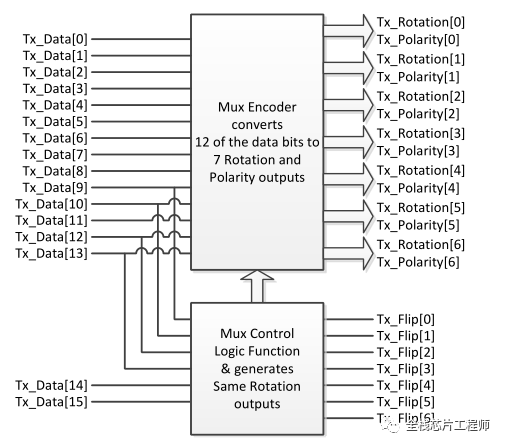

也就是说,CPHY是16 bit 的有效数据要分配成7 个symbols,每个symbols 3bit共计21bit,那么16bit怎么编码成21bit呢?如下图:

详细图如下:

Flip[6:0]的编码逻辑如下:

CPHY的带宽

对于D-PHY而言,以Byte为单位进行数据传输。一个UI是1 bit。

对于C-PHY而言,以16bit为单位进行数据传输,一个UI 是16/7 bit。

16/7 是怎么计算的?见下图:16bit数据映射成21bit,也就是7个symbol,每个symbol有3个bit。

为什么16bit有效数据要分配成7个symbols?

16bit数据,有2^16=65536个值,7个symbol(1个symbol代表5种状态)有5^7=78125个值。所以并不是所有symbol状态都被用完。

若分配为6个symbol,5^6=15625,小于2^16,无法完备表达16bit数据的值。

CPHY的1个lane最大带宽是2.5G symbols/s,即每一lane 最大传输速率是 2.5G UI/s,每一个UI是16/7=2.28bit,CPHY最多有3个lane。因此CPHY最大带宽为2.5G*16/7bit * 3 = 17.14G bit/s。在同样是2.5G的速率下,C-PHY可以达到17.1G,而D-PHY只有10G。

CPHY通信时序

上图与下图区别就是:Programmable Sequence

Escape Mode

非常经典的设计思路,A、C异或得到时钟,时钟上升沿采集A得到命令,Escape Mode可以发送命令、发送数据(低功耗)。

我们来看,Escape Mode包含了哪些命令:

Trigger-Reset Command in Escape Mode

Low-Power Data Transmission

编辑:黄飞

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)