一、PCB概念

PCB(PrintedCircuitBoard),中文名称为印制电路板,又称印刷电路板、印刷线路板,是重要的电子部件,是电子元器件的支撑体,是电子元器件电气连接的提供者。由于它是采用电子印刷术制作的,故被称为“印刷”电路板。

二、PCB在各种电子设备中作用和功能

1.焊盘:提供集成电路等各种电子元器件固定、装配的机械支撑。

2.走线:实现集成电路等各种电子元器件之间的布线和电气连接(信号传输)或电绝缘。提供所要求的电气特性,如特性阻抗等。

3.绿油和丝印:为自动装配提供阻焊图形,为元器件插装、检查、维修提供识别字符和图形。

三、PCB技术发展概要

从1903年至今,若以PCB组装技术的应用和发展角度来看,可分为三个阶段

1、通孔插装技术(THT)阶段PCB

1.金属化孔的作用:

(1).电气互连---信号传输

(2).支撑元器件---引脚尺寸限制通孔尺寸的缩小

a.引脚的刚性

b.自动化插装的要求

2.提高密度的途径

(1)减小器件孔的尺寸,但受到元件引脚的刚性及插装精度的限制,孔径≥0.8mm

(2)缩小线宽/间距:0.3mm—0.2mm—0.15mm—0.1mm

(3)增加层数:单面—双面—4层—6层—8层—10层—12层—64层

2、表面安装技术(SMT)阶段PCB

1.导通孔的作用:仅起到电气互连的作用,孔径可以尽可能的小,堵上孔也可以。

2.提高密度的主要途径

(1).过孔尺寸急剧减小:0.8mm—0.5mm—0.4mm—0.3mm—0.25mm

(2).过孔的结构发生本质变化:

a.埋盲孔结构优点:提高布线密度1/3以上、减小PCB尺寸或减少层数、提高可靠性、改善了特性阻抗控制,减小了串扰、噪声或失真(因线短,孔小)

b.盘内孔(hole in pad)消除了中继孔及连线

(3)薄型化:双面板:1.6mm—1.0mm—0.8mm—0.5mm

(4)PCB平整度:

a.概念:PCB板基板翘曲度和PCB板面上连接盘表面的共面性。

b.PCB翘曲度是由于热、机械引起残留应力的综合结果

c.连接盘的表面涂层:HASL、化学镀NI/AU、电镀NI/AU…

3 芯片级封装(CSP)阶段PCB

CSP开始进入急剧的变革于发展之中,推动PCB技术不断向前发展,PCB工业将走向激光时代和纳米时代。

四、PCB表面涂覆技术

PCB表面涂覆技术是指阻焊涂覆(兼保护)层以外的可供电气连接用的可焊性涂(镀)覆层和保护层。

按用途分类:

1.焊接用:因铜的表面必须有涂覆层保护,不然在空气中很容易氧化。

2.接插件用:电镀Ni/Au或化学镀Ni/Au(硬金,含P及Co)

3.线焊用:wire bonding 工艺

热风整平(HASL或HAL)

从熔融Sn/Pb焊料中出来的PCB经热风(230℃)吹平的方法。

1.基本要求:

(1). Sn/Pb=63/37(重量比)

(2).涂覆厚度至少>3um

(3)避免形成非可焊性的Cu3Sn的出现, Cu3Sn出现的原因是锡量不足,如Sn/Pb合金涂覆层太薄,焊点组成由可焊的Cu6Sn5– Cu4Sn3-- Cu3Sn2—不可焊的Cu3Sn

2.工艺流程

去除抗蚀剂—板面清洁处理—印阻焊及字符—清洁处理—涂助焊剂— 热风整平—清洁处理

3.缺点:

a.铅锡表面张力太大,容易形成龟背现象。

b.焊盘表面不平整,不利于SMT焊接。

化学镀Ni/Au是指PCB连接盘上化学镀Ni(厚度≥3um)后再镀上一层0.05-0.15um薄金,或镀上一层厚金(0.3-0.5um)。由于化学镀层均匀,共面性好,并可提供多次焊接性能,因此具有推广应用的趋势。其中镀薄金(0.05-0.1um)是为了保护Ni的可焊性,而镀厚金(0.3-0.5um)是为了线焊(wire bonding)工艺需要。

1.Ni层的作用:

a.作为Au、Cu之间的隔离层,防止它们之间相互扩散,造成其扩散部位呈疏松状态。

b.作为可焊的镀层,厚度至少>3um

2.Au的作用:

Au是Ni的保护层,厚度0.05-0.15之间,不能太薄,因金的气孔性较大如果太薄不能很好的保护Ni,造成Ni氧化。其厚度也不能>0.15um,因焊点中会形成金铜合金Au3Au2(脆 ),当焊点中Au超过3%时,可焊性变差。

电镀Ni/Au

镀层结构基本同化学Ni/Au,因采用电镀的方式,镀层的均匀性要差一些。

五、PCB设计输出生产文件 注意事项

1.需要输出的层有:

(1).布线层包括顶层/底层/中间布线层;

(2).丝印层包括顶层丝印/底层丝印;

(3).阻焊层包括顶层阻焊和底层阻焊;

(4).电源层包括VCC 层和GND 层;

(5).另外还要生成钻孔文件NCDrill。

2. 如果电源层设置为Split/Mixed ,那么在AddDocument 窗口的Document 项选择RouTIng 并且每次输出光绘文件之前都要对PCB图使用PourManager 的Plane Connect 进行覆铜;如果设置为CAMPlane 则选择Plane 在设置Layer 项的时候要把Layer25 加上在Layer25 层中选择Pads 和Vias。

3. 在设备设置窗口按Device Setup 将Aperture 的值改为199。

4. 在设置每层的Layer 时将BoardOutline 选上。

5. 设置丝印层的Layer 时不要选择PartType 选择顶层底层和丝印层的Outline Text Line。

6. 设置阻焊层的Layer 时选择过孔表示过孔上不加阻焊。一般过孔都会组焊层覆盖。

六、安规标识要求

1. 保险管的安规标识齐全保险丝附近是否有6 项完整的标识,包括保险丝序号、熔断特性、额定电流值、防爆特性、额定电压值、英文警告标识。如F101 F3.15AH,250Vac, “CAUTION:For ConTInuedProtecTIon Against Risk of Fire,Replace Only With SameType and Rating of Fuse” 。若PCB上没有空间排布英文警告标识,可将工,英文警告标识放到产品的使用说明书中说明。

2. PCB上危险电压区域标注高压警示符PCB的危险电压区域部分应用40mil 宽的虚线与安全电压区域隔离,并印上高压危险标识和“ DANGER!HIGHVOTAGE ” 。

3. 原、付边隔离带标识清楚PCB的原、付边隔离带清晰,中间有虚线标识。

4. PCB板安规标识应明确齐全。

七、PCB EMI设计

在PCB设计中最常见的问题就是信号线跨越分割地或电源而产生EMI问题。为规避这种EMI问题下面就为大家介绍一下PCB设计中EMI设计的规范步骤。

1、IC的电源处理

保证每个IC的电源PIN都有一个0.1μF的去耦电容,对于BGA CHIP,要求在BGA的四角分别有0.1μF、0.01μF的电容共8个。对走线的电源尤其要注意加滤波电容,如VTT等。这不仅对稳定性有影响,对EMI也有很大的影响。一般去耦电容还是需要遵循芯片厂家要求。

2、时钟线的处理

1.建议先走时钟线。

2.频率大于等于66M的时钟线,每条过孔数不要超过2个,平均不得超过1.5个。

3.频率小于66M的时钟线,每条过孔数不要超过3个,平均不得超过2.5个

4.长度超过12inch的时钟线,如果频率大于20M,过孔数不得超过2个。

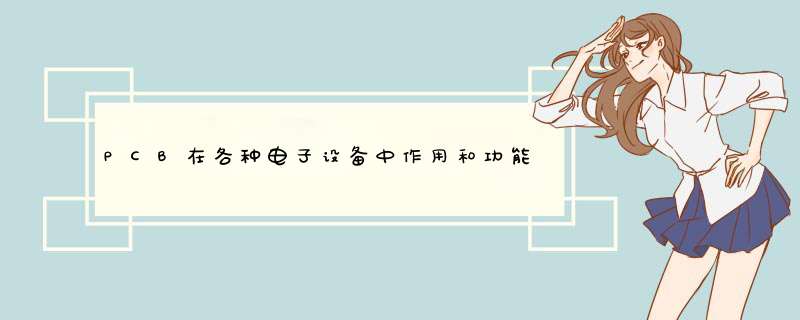

5.如果时钟线有过孔,在过孔的相邻位置,在第二层(地层)和第三层(电源层)之间加一个旁路电容、如图2.5-1所示,以确保时钟线换层后,参考层(相邻层)的高频电流的回路连续。旁路电容所在的电源层必须是过孔穿过的电源层,并尽可能地靠近过孔,旁路电容与过孔的间距最大不超过300MIL。

6.所有时钟线原则上不可以穿岛(跨越分割)。下面列举了穿岛的四种情形。

时钟、复位、100M以上信号以及一些关键的总线信号不能跨分割,至少有一个完整平面,优选GND平面。

时钟信号、高速信号和敏感信号禁止跨分割;

差分信号必须对地平衡,避免单线跨分割。(尽量垂直跨分割)

所有信号的高频返回途径都直接位于相邻层信号线的正下方。在信号下面设置一个实体层可以显著减少信号完整性和时序问题,这个实体层可以为该信号提供直接回路。当走线与层分割交叉不可避免时,应使用一个 0.01 uF 回路电容。如图所示,当使用回路电容时,应尽可能靠近信号线与层分割的交叉点布置回路电容。

6.1 跨岛出现在电源岛与电源岛之间。此时时钟线在第四层的背面走线,第三层(电源层)有两个电源岛,且第四层的走线必须跨过这两个岛.

6.2 跨岛出现在电源岛与地岛之间。此时时钟线在第四层的背面走线,第三层(电源层)的一个电源岛中间有一块地岛,且第四层的走线必须跨过这两个岛。

6.3 跨岛出现在地岛与地层之间。此时时钟线在第一层走线,第二层(地层)的中间有一块地岛,且第一层的走线必须跨过地岛,相当于地线被中断。

6.4 时钟线下面没有铺铜。若条件限制实在做不到不穿岛,保证频率大于等于66M的时钟线不穿岛,频率小于66M的时钟线若穿岛,必须加一个去耦电容形成镜像通路。以图6.1为例,在两个电源岛之间并靠近跨岛的时钟线,放置一个0.1UF的电容。

7.当面临两个过孔和一次穿岛的取舍时,选一次穿岛。

8.时钟线要远离I/O一侧板边500MIL以上,并且不要和I/O线并行走,若实在做不到,时钟线与I/O口线间距要大于50MIL。

9.时钟线走在第四层时,时钟线的参考层(电源平面)应尽量为时钟供电的那个电源面上,以其他电源面为参考的时钟越少越好,另外,频率大于等于66M的时钟线参考电源面必须为3.3V电源平面。

10.时钟线打线时线间距要大于25MIL。

11.时钟线打线时进去的线和出去的线应该尽量远。尽量避免类似图A和图C所示的打线方式,若时钟线需换层,避免采用图E的打线方式,采用图F的打线方式。

12.时钟线连接BGA等器件时,若时钟线换层,尽量避免采用图G的走线形式,过孔不要在BGA下面走,最好采用图H的走线形式。

13.注意各个时钟信号,不要忽略任何一个时钟,包括AUDIO CODEC的AC_BITCLK,尤其注意的是FS3-FS0,虽然说从名称上看不是时钟,但实际上跑的是时钟,要加以注意。

14.Clock Chip上拉下拉电阻尽量靠近Clock Chip。

3、I/O口的处理

1.各I/O口包括PS/2、USB、LPT、COM、SPEAK OUT、 GAME分成一块地,最左与最右与数字地相连,宽度不小于200MIL或三个过孔,其他地方不要与数字地相连。

2.若COM2口是插针式的,尽可能靠近I/O地。

3.I/O电路EMI器件尽量靠近I/O SHIELD。

4.I/O口处电源层与地层单独划岛,且Bottom和TOP层都要铺地,不许信号穿岛(信号线直接拉出PORT,不在I/O PORT中长距离走线)。

4、几点说明

1.对EMI设计规范,设计工程师要严格遵守,EMI工程师有检查的权力,违背EMI设计规范而导至EMI测试FAIL,责任由设计工程师承担。

2.EMI工程师对设计规范负责,对严格遵守EMI设计规范,但仍然EMI测试FAIL,EMI工程师有责任给出解决方案,并总结到EMI设计规范中来。

3.EMI工程师对每一个外设口的EMI测试负有责任,不可漏测。

4.每个PCB设计工程师有对该设计规范作修改的建议权和质疑的权力。EMI工程师有责任回答质疑,对工程师的建议通过实验后证实后加入设计规范。

5.EMI工程师有责任降低EMI设计的成本,减少磁珠的使用个数。

八、PCB设计的ESD抑止

PCB布线是ESD防护的一个关键要素,合理的PCB设计可以减少故障检查及返工所带来的不必要成本。在PCB设计中,由于采用了瞬态电压抑止器(TVS)二极管来抑止因ESD放电产生的直接电荷注入,因此PCB设计中更重要的是克服放电电流产生的电磁干扰(EMI)电磁场效应。本文将提供可以优化ESD防护的PCB设计准则。

1、电路环路

电流通过感应进入到电路环路,这些环路是封闭的,并具有变化的磁通量。电流的幅度与环的面积成正比。较大的环路包含有较多的磁通量,因而在电路中感应出较强的电流。因此,必须减少环路面积。

最常见的环路由电源和地线所形成。在可能的条件下,可以采用具有电源及接地层的多层PCB设计。多层电路板不仅将电源和接地间的回路面积减到最小,而且也减小了ESD脉冲产生的高频EMI电磁场。

如果不能采用多层电路板,那么用于电源线和接地的线必须连接成网格状。网格连接可以起到电源和接地层的作用,用过孔连接各层的印制线,在每个方向上过孔连接间隔应该在6厘米内。另外,在布线时,将电源和接地印制线尽可能靠近也可以降低环路面积。

减少环路面积及感应电流的另一个方法是减小互连器件间的平行通路。

当必须采用长于30厘米的信号连接线时,可以采用保护线。一个更好的办法是在信号线附近放置地层。信号线应该距保护线或接地线层13毫米以内。

将每个敏感元件的长信号线(>30厘米)或电源线与其接地线进行交叉布置。交叉的连线必须从上到下或从左到右的规则间隔布置。

2、电路连线长度

长的信号线也可成为接收ESD脉冲能量的天线,尽量使用较短信号线可以降低信号线作为接收ESD电磁场天线的效率。

尽量将互连的器件放在相邻位置,以减少互连的印制线长度。

3、地电荷注入

ESD对地线层的直接放电可能损坏敏感电路。在使用TVS二极管的同时还要使用一个或多个高频旁路电容器,这些电容器放置在易损元件的电源和地之间。旁路电容减少了电荷注入,保持了电源与接地端口的电压差。

TVS使感应电流分流,保持TVS钳位电压的电位差。TVS及电容器应放在距被保护的IC尽可能近的位置,要确保TVS到地通路以及电容器管脚长度为最短,以减少寄生电感效应。

九、PCB生产中Mark点设计

1.pcb必须在板长边对角线上有一对应整板定位的Mark点,板上集成电路引脚中心距小于0.65mm的芯片需在集成电路长边对角线上有一对对应芯片定位的Mark点;pcb双面都有贴片件时,则pcb的两面都按此条加Mark点。

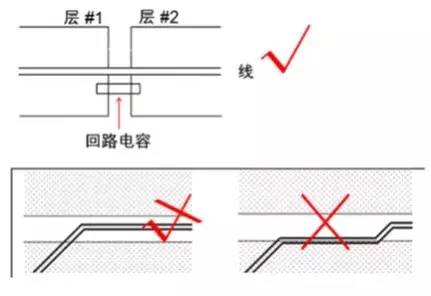

2.pcb边需留5mm工艺边(机器夹持PCB最小间距要求),同时应保证集成电路引脚中心距小于0.65mm的芯片要距离板边大于13mm(含工艺边);板四角用Ф5圆弧倒角。pcb应采用拼板方式,从目前pcb翅曲程度考虑,最佳拼接长度约为200mm,(设备加工尺寸:长度最大为330mm;宽度最大为250mm),在宽度方向尽量不拼以防止在生产过程中弯曲。如下图:

3.MARK点作用及类别

Mark点也叫基准点,为装配工艺中的所有步骤提供共同的可测量点,保证了装配使用的每个设备能精确地定位电路图案。因此,Mark点对SMT生产至关重要

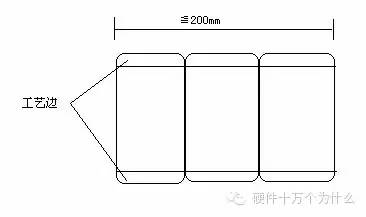

4.我部推荐的MARK点设计规范

1)形状:建议Mark点标记为直径:R=1.0mm实心圆;

2)组成一个完整的MARK点包括:标记点(或特征点)和空旷区域。

3)位置:Mark点位于单板或拼板上的对角线相对位置且尽可能地距离分开;最好分布在最长对角线位置(如MARK点位置图)。

4)为保证贴装精度的要求,SMT要求:每块PCB内必须至少有一对符合设计要求的可供SMT机器识别的MARK点,同时必须有单板MARK(拼板时),拼板MARK或组合MARK只起辅助定位的作用。

5)拼板时,每一单板的MARK点相对位置必须一样。不能因为任何原因而挪动拼板中任一单板上MARK点的位置,而导致各单板MARK点位置不对称;

6)PCB上所有MARK点只有满足:在同一对角线上且成对出现的两个MARK,方才有效。因此MARK点都必须成对出现,才能使用(MARK点位置图)。

7)MARK点(空旷区边缘)距离PCB边缘必须≥5.0mm(机器夹持PCB最小间距要求)(如MARK点位置图)。

(MARK点位置图)

8)尺寸

A.Mark点标记最小的直径为1.0mm,最大直径是3.0mm,Mark点标记在同一块印制板上尺寸变化不能超过25 微米;

B.特别强调:同一板号PCB上所有Mark点的大小必须一致(包括不同厂家生产的同一板号的PCB);

C.建议将所有的Mark点标记直径统一设为1.0mm。

9)空旷区要求

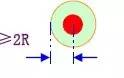

在Mark点标记周围,必须有一块没有其它电路特征或标记的空旷面积。空旷区圆半径 r≥2R , R为MARK点半径,r达到3R时,机器识别效果更好。

10)材料

Mark点标记可以是裸铜、清澈的防氧化涂层保护的裸铜。如果使用阻焊(soldermask),不应该覆盖Mark点或其空旷区域

11)MARK点的光亮度应保持一致。

12)平整度:Mark点标记的表面平整度应该在15 微米之内。

13)对比度

A.当Mark点标记与印制板的基质材料之间有高对比度时可达到最佳的识别性能

B.对于所有Mark点的内层背景必须相同

以下在补点他人这方面的经验,作为参考

MARK点分类:

1)Mark点用于锡膏印刷和元件贴片时的光学定位。根据Mark点在PCB上的作用,可分为拼板Mark点、单板Mark点、局部Mark点(也称器件级MARK点),

2)拼板的工艺边上和不需拼板的单板上应至少有三个Mark点,呈L形分布,且对角Mark点关于中心不对称。

3)如果双面都有贴装元器件,则每一面都应该有Mark点。

4)需要拼板的单板上尽量有Mark点,如果没有放置Mark点的位置,在单板上可不放置Mark点。

5)引线中心距≤0.5 mm的QFP以及中心距≤0.8 mm的BGA等器件,应在通过该元件中心点对角线附近的对角设置局部Mark点,以便对其精确定位。

6)如果几个SOP器件比较靠近(≤100mm)形成阵列,可以把它们看作一个整体,在其对角位置设计两个局部Mark点。

设计说明和尺寸要求:

1)Mark点的形状是直径为1mm的实心圆,材料为铜,表面喷锡,需注意平整度,边缘光滑、齐整,颜色与周围的背景色有明显区别;阻焊开窗与Mark点同心,对于拼板和单板直径为3mm,对于局部的Mark点直径为1mm,

2)单板上的Mark点,中心距板边不小于5mm;工艺边上的Mark点,中心距板边不小于3mm。

3)为了保证印刷和贴片的识别效果,Mark点范围内应无焊盘、过孔、测试点、走线及丝印标识等,不能被V-CUT槽所切造成机器无法辨识。

4)为了增加Mark点和基板之间的对比度,可以在Mark点下面敷设铜箔。同一板上的Mark点其内层背景要相同,即Mark点下有无铜箔应一致。

5)对于单板和拼板的Mark点应当作元件来设计,对于局部的Mark点应作为元件封装的一部分设计。便于赋予准确的坐标值进行定位。

PCB设计之光学基准点!

在有贴片元件的PCB板上,为了对PCB整板进行定位,通常需要在PCB板的四个角放置光学定位点,一般放三个即可。常见的基准点主要有三种:拼板基准点,单元基准点,局部基准点。

基准点结构

(1)拼板基准点和单元基准点

形状/大小:直径为40mil 的实心圆。阻焊开窗:和基准点同心的圆形,大小为基准点直径的两倍。在 2mm直径的边缘处要求有一圆形或八边形的铜线作保护圈用。同一板上的光学定位基准符号其内层背景要相同,即三个基准符号下有无铜箔应一致。

(2)局部基准点

间距≤0.4mm的QFP和间距≤0.8mm BGA、CSP、FC等器件需要放置局部基准点。

大小/形状:直径为40mil 的实心圆。

阻焊开窗:大小按普通焊盘处理,外圈铜环可不要。

基准点放置:

一般原则 :

过SMT设备加工的单板必须放置基准点。单面基准点数量≥3。

单面布局时,只需元件面放置基准点。. A5 I5 ^0 L- z1 m+ P PCB双面布局时,基准点双面放置。双面放置的基准点,除镜像拼板外,正反两面的基准点位置要求基本一致。见下图。

(1) 拼板的基准点放置

拼板需要放置拼板基准点、单元基准点。

拼板基准点和单元基准点数量各为三个。在板边呈“L”形分布,尽量远离。拼板基准点的位置要求见下图A。

采用镜相对称拼板时,辅助边上的基准点必须满足翻转后重合的要求,参见下图B

(2) 单元板的基准点放置

基准点数量为三个,在板边呈“L”形分布,各基准点之间的距离尽量远。基准点距离板边必须大于5mm,如不能保证四个边都满足,则至少要保证传送边满足要求。

十、时钟PCB走线设计的注意事项

布局

时钟晶体和相关电路应布置在PCB的中央位置并且要有良好的地层,而不是靠近I/O接口处。不可将时钟产生电路做成子卡或者子板的形式,必须做在单独的时钟板上或者承载板上。

如下图所示,绿色框中部分下一层最好不要走线

在PCB时钟电路区域只布与时钟电路有关的器件,避免布设其他电路,晶体附近或者下面不要布其他信号线:在时钟发生电路、晶体下使用地平面,若其他信号穿过该平面,违反了映像平面功能,如果让信号穿越这个地平面的话,就会存在很小的地环路并影响地平面的连续性,这些地环路在高频时将会产生问题。

对于时钟晶体、时钟电路,可以采用屏蔽措施进行屏蔽处理;

若时钟外壳为金属,则PCB设计时一定要在晶体下方铺铜,并保证此部分与完整的地平面有良好的电气连接(通过多孔接地)。

时钟晶体下面铺地的好处:晶体振荡器内部的电路会产生射频电流,如果晶体是金属外壳封装的,直流电源脚是直流电压参考和晶体内部射频电流回路参考的依靠,通过地平面释放外壳被射频辐射产生的瞬态电流。总之,金属外壳是一个单端天线,最近的映像层、地平面层有时两层或者更多层做为射频电流对地的辐射耦合作用是足够的。晶体下铺地对散热也是有好处的。

时钟电路和晶体下铺地将提供一个映像平面,可以降低对相关晶体和时钟电路产生共模电流,从而降低射频辐射,地平面对差模射频电流同样有吸收作用,这个平面必须通过多点连接到完整的地平面上,并要求通过多个过孔,这样可以提供低的阻抗,为增强这个地平面的效果,时钟发生电路应该与这个地平面靠近。

SMT封装的晶体将比金属外壳的晶体有更多的射频能量辐射:因为表贴晶体大多是塑料封装,晶体内部的射频电流会向空间辐射并耦合到其他器件。

共用时钟走线

对快速上升沿信号及时钟信号采用辐射状拓扑连接好于采用单个公共驱动源的网络串接,每个走线应该根据其特性阻抗采取端接措施来布线。

时钟传输线要求及PCB分层

时钟走线原则:在紧邻时钟走线层安排完整的映像平面层,减小走线的长度并进行阻抗控制。

错误的跨层走线和阻抗不匹配会导致:

走线使用过孔和跳转导致映像回路的不完整性;

映像平面上由于器件信号管脚上电压随着信号的变化而变化产生的浪涌电压;

如果走线没有考虑3W原则的话,不同时钟信号会引起串扰;

时钟信号的布线

时钟线一定要走在多层PCB板的内层。并且一定要走带状线;如果要走在外层,只能走微带线。

走在内层能保证完整的映像平面,它可以提供一个低阻抗射频传输路径,并产生磁通量,以抵消它们的源传输线的磁通量,源和返回路径的距离越近,则消磁就越好。由于增强了消磁能力,高密PCB板的每个完整平面映像层可提供6-8dB的抑制。

时钟布多层板的好处:有一层或者多层可以专门用于完整的电源和地平面,可以设计成好的去藕系统,减小地环路的面积,降低了差模辐射,减小了EMI,减小了信号和电源返回路径的阻抗水平,可以保持全程走线阻抗的一致性,减小了邻近走线间的串扰等。

十一、PCB叠层设计

在设计多层PCB电路板之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结构,也就是决定采用4层,6层,还是更多层数的电路板。确定层数之后,再确定内电层的放置位置以及如何在这些层上分布不同的信号。这就是多层PCB层叠结构的选择问题。层叠结构是影响PCB板EMC性能的一个重要因素,也是抑制电磁干扰的一个重要手段。本节将介绍多层PCB板层叠结构的相关内容。对于电源、地的层数以及信号层数确定后,它们之间的相对排布位置是每一个PCB工程师都不能回避的话题;

层的排布一般原则:

1、确定多层PCB板的层叠结构需要考虑较多的因素。从布线方面来说,层数越多越利于布线,但是制板成本和难度也会随之增加。对于生产厂家来说,层叠结构对称与否是PCB板制造时需要关注的焦点,所以层数的选择需要考虑各方面的需求,以达到最佳的平衡。对于有经验的设计人员来说,在完成元器件的预布局后,会对PCB的布线瓶颈处进行重点分析。结合其他EDA工具分析电路板的布线密度;再综合有特殊布线要求的信号线如差分线、敏感信号线等的数量和种类来确定信号层的层数;然后根据电源的种类、隔离和抗干扰的要求来确定内电层的数目。这样,整个电路板的板层数目就基本确定了。

2、元件面下面(第二层)为地平面,提供器件屏蔽层以及为顶层布线提供参考平面;敏感信号层应该与一个内电层相邻(内部电源/地层),利用内电层的大铜膜来为信号层提供屏蔽。电路中的高速信号传输层应该是信号中间层,并且夹在两个内电层之间。这样两个内电层的铜膜可以为高速信号传输提供电磁屏蔽,同时也能有效地将高速信号的辐射限制在两个内电层之间,不对外造成干扰。

3、所有信号层尽可能与地平面相邻;

4、尽量避免两信号层直接相邻;相邻的信号层之间容易引入串扰,从而导致电路功能失效。在两信号层之间加入地平面可以有效地避免串扰。5、主电源尽可能与其对应地相邻;

6、兼顾层压结构对称。

7、对于母板的层排布,现有母板很难控制平行长距离布线,对于板级工作频率在50MHZ以上的(50MHZ以下的情况可参照,适当放宽),建议排布原则:

元件面、焊接面为完整的地平面(屏蔽);

无相邻平行布线层;

所有信号层尽可能与地平面相邻;

关键信号与地层相邻,不跨分割区。

注:具体PCB的层的设置时,要对以上原则进行灵活掌握,在领会以上原则的基础上,根据实际单板的需求,如:是否需要一关键布线层、电源、地平面的分割情况等,确定层的排布,切忌生搬硬套,或抠住一点不放。

8、多个接地的内电层可以有效地降低接地阻抗。例如,A信号层和B信号层采用各自单独的地平面,可以有效地降低共模干扰。

常用的层叠结构:

4层板

下面通过 4 层板的例子来说明如何优选各种层叠结构的排列组合方式。

对于常用的 4 层板来说,有以下几种层叠方式(从顶层到底层)。(1)Siganl_1(Top),GND(Inner_1),POWER(Inner_2),Siganl_2(Bottom)。(2)Siganl_1(Top),POWER(Inner_1),GND(Inner_2),Siganl_2(Bottom)。

(3)POWER(Top),Siganl_1(Inner_1),GND(Inner_2),Siganl_2(Bottom)。显然,方案 3 电源层和地层缺乏有效的耦合,不应该被采用。那么方案 1 和方案 2 应该如何进行选择呢?一般情况下,设计人员都会选择方案 1 作为 4层板的结构。选择的原因并非方案 2 不可被采用,而是一般的 PCB 板都只在顶层放置元器件,所以采用方案 1 较为妥当。但是当在顶层和底层都需要放置元器件,而且内部电源层和地层之间的介质厚度较大,耦合不佳时,就需要考虑哪一层布置的信号线较少。对于方案 1而言,底层的信号线较少,可以采用大面积的铜膜来与 POWER 层耦合;反之,如果元器件主要布置在底层,则应该选用方案 2 来制板。如果采用如图 11-1 所示的层叠结构,那么电源层和地线层本身就已经耦合,考虑对称性的要求,一般采用方案 1。

6层板

在完成 4 层板的层叠结构分析后,下面通过一个 6 层板组合方式的例子来说明 6 层板层叠结构的排列组合方式和优选方法。(1)Siganl_1(Top),GND(Inner_1),Siganl_2(Inner_2),Siganl_3(Inner_3),POWER(Inner_4),Siganl_4(Bottom)。方案 1 采用了 4 层信号层和 2 层内部电源/接地层,具有较多的信号层,有利于元器件之间的布线工作,但是该方案的缺陷也较为明显,表现为以下两方面。① 电源层和地线层分隔较远,没有充分耦合。② 信号层 Siganl_2(Inner_2)和 Siganl_3(Inner_3)直接相邻,信号隔离性不好,容易发生串扰。(2)Siganl_1(Top),Siganl_2(Inner_1),POWER(Inner_2),GND(Inner_3),Siganl_3(Inner_4),Siganl_4(Bottom)。方案 2 相对于方案 1,电源层和地线层有了充分的耦合,比方案 1 有一定的优势,但是 Siganl_1(Top)和 Siganl_2(Inner_1)以及 Siganl_3(Inner_4)和 Siganl_4(Bottom)信号层直接相邻,信号隔离不好,容易发生串扰的问题并没有得到解决。(3)Siganl_1(Top),GND(Inner_1),Siganl_2(Inner_2),POWER(Inner_3),GND(Inner_4),Siganl_3(Bottom)。相对于方案 1 和方案 2,方案 3 减少了一个信号层,多了一个内电层,虽然可供布线的层面减少了,但是该方案解决了方案 1 和方案 2 共有的缺陷。① 电源层和地线层紧密耦合。② 每个信号层都与内电层直接相邻,与其他信号层均有有效的隔离,不易发生串扰。③ Siganl_2(Inner_2)和两个内电层 GND(Inner_1)和 POWER(Inner_3)相邻,可以用来传输高速信号。两个内电层可以有效地屏蔽外界对 Siganl_2(Inner_2)层的干扰和Siganl_2(Inner_2)对外界的干扰。

综合各个方面,方案 3 显然是最优化的一种,同时,方案 3 也是 6 层板常用的层叠结构。通过对以上两个例子的分析,相信读者已经对层叠结构有了一定的认识,但是在有些时候,某一个方案并不能满足所有的要求,这就需要考虑各项设计原则的优先级问题。遗憾的是由于电路板的板层设计和实际电路的特点密切相关,不同电路的抗干扰性能和设计侧重点各有所不同,所以事实上这些原则并没有确定的优先级可供参考。但可以确定的是,设计原则 2(内部电源层和地层之间应该紧密耦合)在设计时需要首先得到满足,另外如果电路中需要传输高速信号,那么设计原则 3(电路中的高速信号传输层应该是信号中间层,并且夹在两个内电层之间)就必须得到满足。

10层板

PCB典型10层板设计

一般通用的布线顺序是TOP--GND---信号层---电源层---GND---信号层---电源层---信号层---GND---BOTTOM

本身这个布线顺序并不一定是固定的,但是有一些标准和原则来约束:如top层和bottom的相邻层用GND,确保单板的EMC特性;如每个信号层优选使用GND层做参考平面;整个单板都用到的电源优先铺整块铜皮;易受干扰的、高速的、沿跳变的优选走内层等等。

下表给出了多层板层叠结构的参考方案,供参考。

PCB设计之叠层结构改善案例(From金百泽科技)

问题点

产品有8组网口与光口,测试时发现第八组光口与芯片间的信号调试不通,导致光口8调试不通,无法工作,其他7组光口通信正常。

1、问题点确认

根据客户端提供的信息,确认为L6层光口8与芯片8之间的两条差分阻抗线调试不通;

2、客户提供的叠构与设计要求

改善措施

影响阻抗信号因素分析:

线路图分析:客户L56层阻抗设计较为特殊,L6层阻抗参考L5/L7层,L5层阻抗参考L4/L6层,其中L5/L6层互为参考层,中间未做地层屏蔽,光口8与芯片8之间线路较长,L6层与L5层间存在较长的平行信号线(约30%长度)容易造成相互干扰,从而影响了阻抗的精准度,阻抗线的设计屏蔽层不完整,也造成阻抗的不连续性,其他7组部分也有相似问题,但相对较轻微。

L56层存在特殊设计(均为信号层,存在差分阻抗平行设计、相邻阻抗层间未设计参考地层),客户端未充分考虑相邻层走线存在的干扰,导致调试不通问题。

与客户沟通对叠层进行优化,将L45、L56、L67层结构进行了调整,介质层厚度分别由20.87mil、6mil、13mil 调整为5.12mil、22.44mil、5.12mil,将而L4、L7间的参考地层间的距离拉近,L56层互为参考且屏蔽不足的线路层距离拉远,减少干扰。

优化后的叠层结构:

优化后的阻抗匹配:

改善效果

通过调整叠层结构,拉大L56层相邻信号层之间的距离,串扰造成的系统故障问题得到解决。

编辑:黄飞

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)