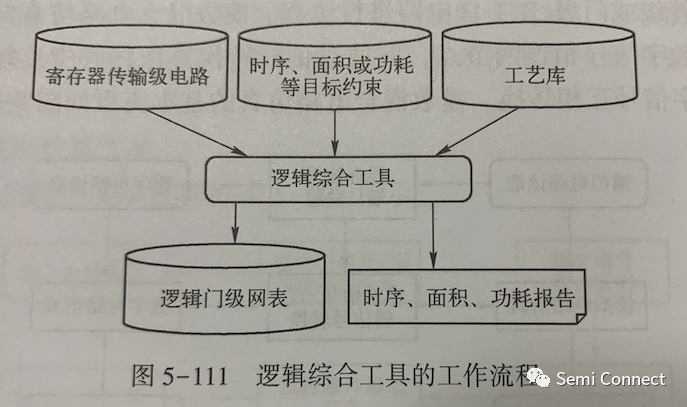

逻辑综合工具(Logic Synthesizer)是将数字电路的寄存器传输级(RTL)描述经过布尔函数简化和逻辑优化等步骤自动转换到逻辑门级网表的工具。逻辑综合工具的工作流程如图5-111所示。

逻辑综合工具的输入有以下3方面。

(1)Verilog或VHDL硬件描述语言所描述的寄存器传输级电路。

(2)时序、面积或功耗等目标约束(Constraints)。

(3)集成电路逻辑组件工艺库(Libraries)。此工艺库通常包含与、或、异或、与非、寄存器等逻辑门。

逻辑综合工具将寄存器传输级电路描述根据所设定的各类目标约束进行如下编译、综合及优化。

(1)从Verilog或VHDL硬件描述语言编译至与工艺组件无关的初始电路。

(2)执行算法逻辑(加、减、乘、除及复杂的组合运算)优化。例如,乘法器有多种实现方式, 相应地会产生多种时序、功耗及面积,如何根据目标设定选出最合适的结构将对最后的综合结果有重大影响。

(3)与工艺无关的时序逻辑及组合逻辑优化。时序逻辑优化主要对有限状态机(Finite State Machine)及寄存器进行优化,组合逻辑优化主要对布尔函数进行优化。

(4)将优化完的时序及组合逻辑转换成逻辑门级的电路网表。此时因各个逻辑门有准确的时序、功耗及面积数据,即可执行与工艺有关的最后优化。

完成上述过程后,逻辑综合工具即生成经过优化的逻辑门级电路网表,输出的门级电路网表的逻辑功能必须与原有寄存器传输级电路功能保持一致。

随着集成电路规模的不断增大和制造工艺尺寸的不断减小,为了更准确地评估芯片的时序和面积,逻辑综合工具需预先考虑后段布局布线效应以实现前后段设计的一致性。同时,为了提高逻辑综合工具运行效率,逻辑综合工具必须采用层次化及并行技术实现。

审核编辑 :李倩

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)