有时,微控制器本身可以完全满足设计的所有功能要求。对于大多数嵌入式系统设计,编程良好、高度集成的嵌入式处理器是工程师可用的最具成本效益、最节能、最快的解决方案。

当原始性能至关重要时,专用硬件中捕获的逻辑可以实现最高水平的性能。例如,定序器可以比在软件中实现的相同逻辑快一个数量级。

由于分立逻辑器件占用大量空间和功率,添加 FPGA 可能是一种可行的替代方案;在许多情况下,FPGA 和微控制器的组合是一个很好的解决方案。当微在 FPGA 的逻辑中实现时,更密集的解决方案是可能的。作为硬编码宏,或在每个新设计中被替换和路由的软宏,将整个微控制器吸收到 FPGA 内部不仅可以产生最高的密度,而且可以产生最大的灵活性,特别是如果你有足够的勇气去实际修改核心以提高性能。

本文着眼于在现成的 FPGA 中愉快地运行的微内核。这些可从各种来源获得,包括开放式和封闭式、免费和 IP 许可的。

比原来的更好

遗留和专有架构都可以使用,并且各有优势。旧版内核与旧版 micros 兼容,并提供熟悉的架构。然后,您公司生产的产品可以使用已经过测试和验证的代码。当需要下一代产品甚至新的改进模型时,组织良好且可靠的代码库的可重用性可以节省大量时间。

几个流行的内核已经以原始逻辑形式用于各种 FPGA 系列,包括处理器,例如Microchip PIC、英特尔 8051、Atmel AVR、摩托罗拉 6502、英特尔 8080 和Zilog Z80 微控制器,仅举几例。

一个不那么明显的优点是能够改进初始架构。如果时间和资源允许,可以克服缺点,因为您可以修改设计。例如,非常流行的 8051 架构最初是采用顺序架构引入的,每条指令需要 12 个时钟周期。精确的遗留实现可以反映初始功能,或者可以实现更现代的风格,减少每条指令的时钟周期数。

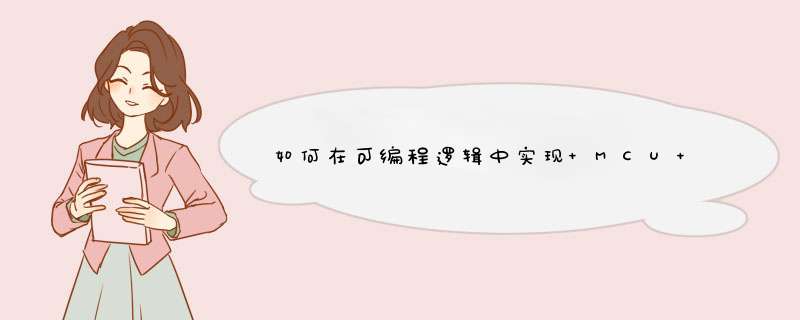

8051 的改进 IP 内核也可用于跨平台开发。R8051XC2-BF 内核¹可用于 ASIC 或Xilinx和Altera FPGA;它通过添加第二个数据指针(初始设计的一个缺点)和 JTAG 调试接口(图 1)对初始设计进行了改进。

图 1:传统内核的商用实现通常会改进最初的分立设计。这个 8051 内核每条指令运行一个时钟,并添加了 JTAG 和第二个数据指针。

ARM 内核

虽然许多设计可以使用 8 位内核,但现代功能可能需要更高的总线宽度来简化处理。如果您正在处理 24 位宽的图形数据,则单个 32 位传输比三个 8 位传输更有效。

也许最流行的 32 位架构是 ARM® Cortex™,毫无疑问,它已成为流行且得到良好支持的 FPGA 实现架构。从面积和功耗的角度来看,ARM Cortex 非常高效。众多工具和开发套件以及用于外围设备、内存管理、数学和 DSP 功能的开源代码都很好地支持可扩展架构。

ARM 内核的一个很好的特性是它们不是某个 FPGA 制造商专有的,并且可以在不同制造商的设备上实现。这意味着随着设计的发展或需求的变化,您不会被锁定在一个供应商中。

另一个好处是架构从更简单、功能更弱的Cortex M0扩展而来高达非常高端的多核A8和A9口味。这还带来了经过轨道验证的驱动程序和堆栈的好处,这些驱动程序和堆栈适用于 USB、以太网、Wi-Fi、ZigBee、蓝牙等高端外围设备。

Xilinx 系列器件是嵌入式微核的大力支持者,ARM 架构也不例外。XC5VLX50-1FFG676C等部件是流行的 Xilinx Virtex® 5的一部分系列,并且是可以在芯片上容纳快速和密集系统的非常大、密集和高端 FPGA 的示例。550 MHz 部件具有 440 个 I/O 和超过 46,000 个逻辑块,不仅支持 ARM 内核功能,还支持高达 72 位宽的存储器宽度、流水线 *** 作、FIFO、具有高达 16.4 Mb 内部块存储器的双端口存储器和 DSP 功能。

Microsemi是另一家提供 ARM 内核支持的 FPGA 制造商,ProASIC3系列是一个很好的目标技术,具有令人印象深刻的低端到高端逻辑、I/O、RAM 和 15,000 到 3,000,000 门数。一个很好的例子是具有 341 I/O 和 516 Kb 内部 RAM 的A3PE3000-FGG484 。

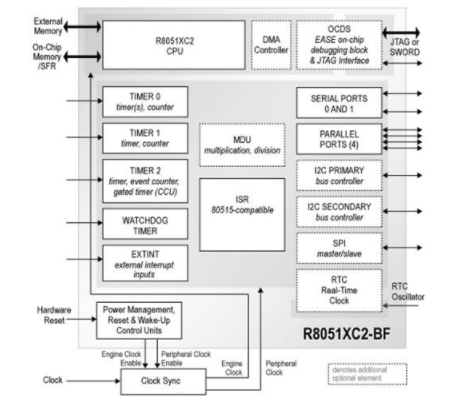

Altera 有类似的部件,如EP3SL50F780C4N,它同样支持 ARM 核心处理器,还为 DDR、DDR2、DDR3、SDRAM 等提供内存支持,最多可在 24 个模块化 I/O bank 上使用 448 个 I/O(该系列中最多 744 个)。作为StraTIx® III系列的一员,Altera 提供对 Altera Mega-FuncTIon Partner Program (AMPP) 的访问,以获得可用的外设、内核和支持。Altera 还通过其 Altera MegaCore 功能支持多种知识产权(图 2)。

图 2:高端 32 位 ARM 架构是许多 FPGA 的流行内核。这个 Altera 版本增加了多核调试和跟踪功能,简化了单个 FPGA 内多个实例化处理器内核的设计。

专有内核

除了行业标准的微控制器内核之外,FPGA 制造商还提供专有内核,这些内核逻辑效率非常高,可扩展至 8 至 32 位性能级别。这些供应商的关键是不要在不需要的功能和外围设备上浪费逻辑;如此经常缩减,实现了准系统处理单元,以提供基本的可编程性和与 FPGA 内部大型逻辑池的接口。这不仅可以让内核快速运行,还可以让它们足够小,以便在您的 SoC 内创建您自己的双核、四核甚至八核处理器。

Xilinx 将此类内核指定为 Blaze,提供 PicoBlaze 和 MicroBlaze 两种风格。PicoBlaze 是一种 8 位 RISC 架构,具有高达 240 MHz 的性能。它主要设计用于 VHDL 设计流程,并作为 VHDL 源文件提供。一旦在 13 个不同的 Xilinx 系列之一中实现,它就不需要外部组件,并且完全在主机部分内运行。

支持的系列包括Kinetex-7、ArTIx-7、Virtex(4、5、6、7、II-Pro)和Spartan®(3 和 6)。

从资源和复杂性的角度来看,PicoBlaze 相当斯巴达(双关语)。它具有一个 16 x 字节宽的通用数据寄存器、1K 的可编程片上程序存储(在 FPGA 配置期间自动加载)、一个字节宽的算术逻辑单元 (ALU),带有 CARRY 和 ZERO 指示标志,64 字节内部暂存器 RAM,以及 256 个输入和 256 个输出端口,便于扩展和增强。

另一方面,它具有可预测的性能,每条指令总是两个时钟周期,最高可达 240 MHz(或在 Virtex-4 FPGA 中为 100 MIPS)和 88 MHz(或在 Spartan-3 FPGA 中为 44 MIPS)。PicoBlaze 对 Xilinx 用户免费,并附带一个汇编程序和 VHDL 源代码。

高端的是 Xilinx MicroBlaze。这是一个 32 位 RISC 哈佛架构软处理器内核,具有 32 个通用 32 位寄存器、ALU、针对嵌入式应用程序优化的丰富指令集、三级 MMU/MPU 支持等。

该内核的灵活性(图 3)允许您选择性能优化的五级流水线,通过 KineTIx-7 系列(如XC7K70T-1FBG676C)或 3 级流水线区域可实现高达 317 DMIPS在 Kintex-7 或 Virtex-6 和 7 系列部件(如XC6VLX130T-1FFG784C)上仍可实现可观的 264 DMIPS 的优化版本。

图 3:Xilinx FPGA 的专有 32 位 MicroBlaze 内核具有条件编译指令,允许您添加所需的模块并删除不需要的模块,以节省逻辑并提高密度。

Altera 还提供了一个称为 NIOS 的专有内核,现在是第二代NIOS II版本(图 4)。它被誉为业内使用最广泛的软处理器,具有实时性能、功率灵敏度和安全关键 (DO-254) 合规性。

图 4:Altera 的第二代 NIOS II 内核被吹捧为 FPGA 使用和支持最广泛的 IP 内核,并带来了许多开发和调试功能。

六级流水线 NIOS 内核可以用少至 600 个逻辑元件和特征向量中断控制、紧密的内存和 DSP 耦合以及添加自定义指令(最多 256 个)的能力来实现。它可以使用内存管理单元 (MMU),并支持开源和商业支持版本的嵌入式 Linux。

可行的替代方案

您的设计细节将决定您应该选择硬宏还是软宏。硬宏占用 FPGA 内部的特定位置和资源,但硬编码宏具有更好的特性,可以实现更好的性能。

软宏也可以实现良好的性能,特别是如果您有足够的勇气修改、改进或并行它们。与往常一样,良好的设计实践将产生最佳结果。

总之,当需要尽可能高的密度和/或性能时,选择 FPGA 内部的软处理器而不是传统的微控制器及其所有支持电路在灵活性、效率、性能、功率、和空间。

有关本文中提到的部件的更多信息,请使用提供的链接访问 Digi-Key 网站上的产品信息页面。

参考

R8051XC2 (Cast Inc.),高性能、可配置、8051 兼容、8 位微控制器内核

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)