本文讨论了可组合的服务器架构、异构计算以及CXL 标准的版本 1、2 和3。

编译来源:semianalysis

随着每一家主要的半导体和数据中心公司都加入了该标准,第一代设备即将发布,Compute Express Link (CXL) 的吸引力正在达到临界点。第 3 代 Compute Express Link (CXL) 规范刚刚发布,它带来了该标准先前版本中缺少的一些重大更改。本文讨论了可组合的服务器架构、异构计算以及 CXL 标准的版本 1、2 和 3。

过去,数据中心芯片主要是为了构建更好的 CPU 内核和更快的内存。十年前的服务器大多看起来与今天的服务器相同。在过去十年中,随着横向扩展和云计算的出现,这场战斗发生了变化。最快的核心不是优先级。重点是如何经济高效地提供总体计算性能并将其连接在一起。

这些趋势都指向计算资源专业化的趋势。收益递减定律的最终示例之一是,在通用 CPU 性能上花费的每个增量晶体管都会带来越来越少的性能。异构计算占主导地位,因为专用ASIC 可以在使用更少晶体管的特定任务中提供超过10 倍的性能。

为每个工作负载设计具有精确计算资源的特定芯片非常昂贵。因为光掩模设置成本、验证和确认,设计芯片的固定成本正在飙升。与其为整个工作负载设计芯片,不如为计算类别设计芯片并将它们连接到特定工作负载所需的任何配置中,这将更具成本效益。

Gordon Moore 博士在预测“摩尔定律”的原始论文中说,用较小的功能构建大型系统可能会更经济,这些功能分别打包和互连。大功能的可用性与功能设计和构造相结合,应该允许大型系统的制造商快速且经济地设计和构造大量不同的设备。

之前,服务器内的芯片连接通常使用 PCI Express 完成。最大的缺点是这个标准缺乏缓存一致性和内存一致性。这两个概念的非技术类比是,如果考虑像邮局这样的服务器。信件是异步的,通常是在新信息使包含原始信息的信件过时之后的几天。连贯性有助于管理和平衡这一点。

使用 PCI Express,从性能和软件的角度来看,不同设备之间通信的开销相对较高。此外,连接多个服务器通常意味着使用以太网或 InfiniBand。这些通信方法共享所有相同的问题,并且具有更差的延迟和更低的带宽。

2018 年,IBM 和英伟达将NVLink 的 PCI Express 缺陷解决方案引入了当时世界上最快的超级计算机Summit。AMD 在FronTIer超级计算机中拥有类似的专有解决方案,称为 Infinity Fabric。没有任何行业生态系统可以围绕这些专有协议发展。CCIX 在 2010 年代中期成为潜在的行业标准,但它从未真正起飞,因为尽管得到了 AMD、赛灵思、华为、Arm 和Ampere CompuTIng 的支持,但它缺乏关键的行业支持。

英特尔拥有超过 90% 的 CPU 市场份额,因此如果没有他们的支持,任何解决方案都不会成功。英特尔正在制定自己的标准,并于 2019 年将其专有规范作为 Compute Express Link (CXL)1.0 捐赠给了新成立的 CXL 联盟。该标准得到了半导体行业大多数最大买家的同时支持。CXL 通过使用其物理层和电气层来搭载 PCIe 5.0 的现有生态系统,但使用改进的协议层,为加载存储内存事务增加一致性和低延迟模式。

由于建立了行业中大多数主要参与者都支持的行业标准协议,CXL 使向异构计算的过渡成为可能。现在业界有一个标准的互连来将这些不同的芯片连接在一起。

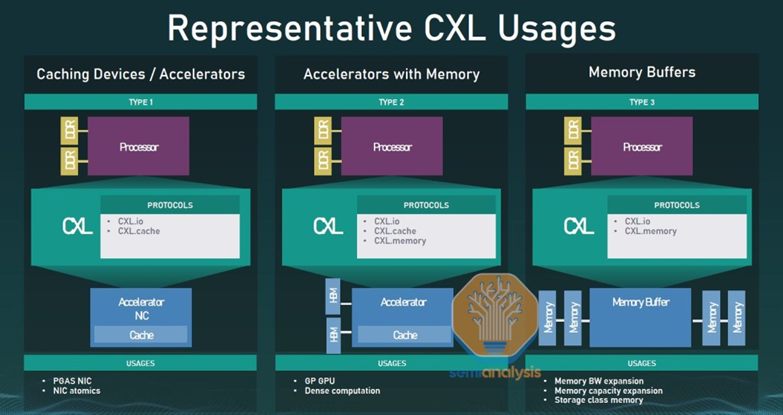

AMD 的 Genoa 和 Intel 的 Sapphire Rapids 将在 2022 年末/2023 年初支持 CXL 1.1。CXL1.1 附带 3 个支持桶,CXL.io、CXL.cache 和 CXL.mem。CXL.io可以被认为是标准 PCIe 的一个类似但改进的版本。CXL.cache允许 CXL 设备连贯地访问和缓存主机 CPU 的内存。CXL.mem 允许主机 CPU 连贯地访问设备的内存。更详细的解释包含在下面的要点中。大多数 CXL 设备将使用 CXL.io、CXL.cache和 CXL.mem 的组合。

CXL.io 是用于初始化、链接、设备发现和枚举以及注册访问的协议。它为 I/O 设备提供接口,类似于 PCIe Gen5。CXL 设备也必须支持 CXL.io。

CXL.cache 是定义主机(通常是 CPU)和设备(例如 CXL 内存模块或加速)之间交互的协议。由于安全使用其本地副本,这允许连接的 CXL 设备以低延迟缓存主机内存. 把这想象成一个 GPU 直接从 CPU 的内存中缓存数据。

CXL.memory / CXL.mem 是为主机处理器(通常是CPU)提供使用加载/存储命令直接访问设备附加内存的协议。将其视为使用专用存储类内存设备的 CPU 或使用 GPU/加速设备上的内存。

到目前为止,我们主要讨论的是异构计算,但 CXL 的真正关键在于内存。

数据中心存在大量内存问题。自 2012 年以来,核心数量迅速增长,但每个核心的内存带宽和容量并未相应增加。自2012 年以来,每个内核的内存带宽有所下降,并且这种趋势将在未来继续。此外,直连 DRAM 和 SSD 在延迟和成本方面存在巨大差距。最后,昂贵的内存资源往往利用率很低,这是一个杀手锏。低利用率对于任何资本密集型行业来说都是一个很大的拖累,而数据中心业务是全球资本最密集的行业之一。

微软表示,50% 的服务器总成本仅来自 DRAM。尽管 DRAM 成本高昂,但高达25% 的DRAM 内存被搁置!简单来说,微软 Azure 总服务器成本的 12.5% 是无所作为。

假设一下,如果此内存可以改为存在于连接的网络上,并跨多个 CPU 和服务器动态分配给虚拟机,而不是坐在每个 CPU 上。内存带宽可以根据工作负载的需求增长和缩小,这将大大提高利用率。

这个概念不仅限于内存,还包括所有形式的计算和网络。可组合的服务器架构是指服务器被分解成各种组件并放置在组中,这些资源可以动态地动态分配给工作负载。

数据中心机架成为计算单元。客户可以为其特定任务选择任意数量的内核、内存和 AI 处理性能。或者更好的是,谷歌、微软、亚马逊等云服务提供商可以根据他们正在运行的工作负载类型任意向他们的客户分配资源,并仅根据他们使用的内容向客户收费。

这一愿景是服务器设计和云计算的圣杯。有许多与此相关的复杂工程问题;许多人集中在构建网络以连接所有内容的延迟和成本上。这些必须严格检查,但协议必须放在第一位,这就是 CXL 2.0 和 3.0 带来的。

CXL 2.0 的主要特性是支持内存池和切换。CXL 交换机可以连接多个主机和设备,从而使连接在 CXL 网络上的设备数量显着增长。新的多逻辑设备功能允许众多主机和设备全部链接并相互通信,而无需历史规定的主从关系。资源网络将由结构管理器进行编排,结构管理器是用于控制和管理该系统的标准 API。细粒度的资源分配、热插拔和动态扩容允许硬件在各个主机之间动态分配和转移,无需任何重启。

从上边的图片可以看出,多台主机可以连接到交换机。然后将交换机连接到各种设备,SLD(单个逻辑设备)或 MLD(多个逻辑设备)。MLD 旨在耦合到多个主机以进行内存池。

MLD 显示为多个 SLD。这允许他们在主机之间汇集内存,甚至汇集加速计算资源。FM(结构管理器)位于控制平面中。它是协调器,分配内存和设备。结构管理器可以位于单独的芯片上或交换机中;它不需要高性能,因为它从不接触数据平面。如果该 CXL 设备是多头的并连接到多个主机的根端口,则这也可以在没有交换机的情况下实现。

将所有这些结合在一起,微软展示了通过池化 DRAM 将部署的 DRAM 减少10% 并节省 5% 的总服务器成本的潜力。这是在没有使用CXL 开关的第一代 CXL 解决方案上。

CXL 3.0 带来了更多改进,有助于扩展创建异构可组合服务器架构的能力。主要关注点是将CXL 从服务器规模扩展到机架规模。这是通过从主机设备模型转变为使 CPU 成为网络上的另一个设备来实现的。

CXL 交换机现在可以支持一系列拓扑。以前在 CXL 2.0 中,只能使用 CXL.mem 设备进行扇出。一个机架或多个服务器机架现在可以通过叶和主干或所有拓扑联网。CXL 3.0 的设备/主机/交换机/交换机端口的理论限制为 4096。这些变化极大地扩大了 CXL 网络的潜在规模,从几台服务器扩展到了许多服务器机架。

此外,所有类型的多个设备都可以位于来自主机的 CXL 的单个根端口上。这以前是一个主要限制,因为单个根端口只能寻址单个设备类型。如果主机连接到具有单个 CXL 根端口的交换机,则该主机只能访问位于交换机外的一种类型的设备。

CXL 3.0 中最重要的变化是内存共享和设备到设备的通信。主机 CPU 和设备现在可以在相同的数据集上协同工作,而无需不必要地打乱和复制数据。一个例子是常见的 AI 工作负载,例如 Google 和Meta 等巨头采用的数十亿参数的深度学习推荐系统。相同的模型数据在许多服务器上重复。用户的请求进来,推理 *** 作开始运行。如果存在 CXL 3.0 内存共享,则大型 AI 模型可以存在于几个中央内存设备中,并且有许多其他设备可以访问它。该模型可以使用实时用户数据不断进行训练,并且可以跨 CXL 交换网络推送更新。这可以将 DRAM 成本降低一个数量级并提高性能。

内存共享可以提高性能和经济性的领域几乎是无限的。第一代内存池可以将总 DRAM 需求降低 10%。较低延迟的内存池可以使多租户云中的节省达到约 23%。内存共享可以将 DRAM 需求降低 35% 以上。这些节省意味着每年在数据中心 DRAM 上花费数十亿美元。

编辑:黄飞

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)