导言

本期主要给大家带来优秀的risc的处理器,前面推荐过几个比如阿里的开源cpu以及zipcpu,大家可以到开源集合中查看,本次推荐几个全面的项目。包含systemverilog以及verilog和VHDL。其中VHDL的开源项目比较少,这个语言主要是欧洲在用,在国内不是特别主流,本次提供一个还不错的项目给对VHDL语言有需求的朋友。

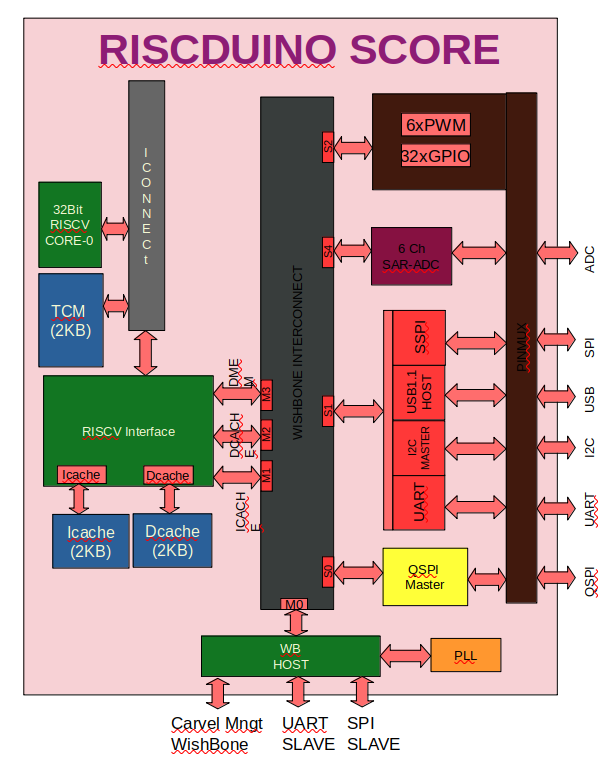

riscduino

32bit的RISC-V的SOC,接口资源包含QSPI,UART,I2C主机,6通道的ADC,6xPWM,3xTImer。总线使用的是Wishbone,代码部分Verilog,部分System Verilog,非常全面的工程,在FPGA中做过映射测试。

Riscduino_Soc

riscduino_layout

开源项目遵循Apache-2.0,

lowRISC

32bit,RISC-V的CPU,相比较前一个的risc,资料略少,但仍然是个不错的项目,习惯systemverilog可以参考学习。

lowrisc

tb

neorv32

32bit的RISC-V,语言是VHDL,相比较而言,VHDL的项目网络上比较少见,该Soc提供UART,IIC以及SPI接口。综合结果如下:

neorv32_processor

审核编辑:刘清

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)