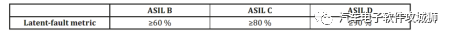

从功能安全的角度来说, ISO26262-2018的第5章节对安全相关的Component提出了SFM, LFM的要求, 下表为不同ASIL等级的组件其LFM潜在失效的量化指标:

TC3xx的LBIST就是针对芯片的逻辑电路部分设计的硬件自检流程, 一般上电的时候触发LBIST检测, 检测结果可用于应用软件对潜在失效的判断, 如是否进入MCU的某种安全状态. 此外, TC3xx还有PBIST(电源自检), MBIST(Memory自检), MONBIST(二级电压监控自检)等.

本文主要介绍LBIST, 即TC3xx的逻辑自检功能.

01 LBIST逻辑自检的检测范围

LBIST检测的范围主要包括以下内容:

1) 所有数字模块, 除了PMS子模块

2) 所有的安全机制的检测(因此, 不需要额外的软件来Cover这部分安全机制)

值得注意的是, LBIST虽然不检测SRAM, PFLASH以及DFLASH(这些是MBIST测试的内容), 但是, SRAM的冗余寄存器在Scan Chain里面, 因此LBIST测试执行完成之后 , SRAM的内容是不可靠的, 需要被重新初始化. 默认情况下, SRAM会在冷启动复位的时候被重新初始化(除非改变HF_PROCONRAM.RAMIN的配置)

02 LBISTController的结构和工作过程

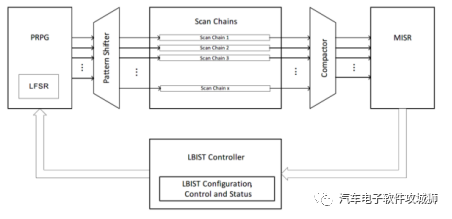

一般的BIST测试电路包括三部分内容, TPG(Test Pattern GeneraTIon), ORA(Output Response Analyzer), 以及BIST Controller. 在我们TC3xx中, 其对应关系如下:

TRG---TC3xx采用的是伪随机Pattern发生器PRPG, 通过LFSR(线性反馈移位寄存器)来产生伪随机的测试向量

ORA---Compactor + MISR, Compactor模块可以对测试的结果通过异或门进行压缩, 并最终产生MISR签名. 用于与期望的签名值进行比较

BIST Controller --- LBIST Controller, 包含了几个主要的LBIST控制寄存器, 来实现诸如Seed, Pattern等参数的配置.

客户在使用的时候, 需要配置LBISTCTRLx(x=0-3)这四个寄存器, 然后通过BMI的方式或者软件触发的方式来开启LBIST测试, 之后会通过STUMPS的结构来实现LBIST测试, PRPG开始对Pattern进行转换, 通过Scan Chains进行电路的测试, 测试的结构经过压缩后从MISR(多输入签名寄存器)输出测试的签名结果, 存放在相应的寄存器当中, 用于客户与理想的签名进行比较, 从而判断LBIST测试是否成功.

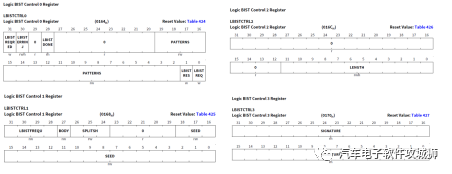

LBISTCTRLx寄存器

LBISTCTRLx(0-3)的定义如下图:

其中比较关键的几个寄存器的位如下:

1) LBISTCTRL0.PATTERNS: 决定执行的LBIST Pattern的个数.

2) LBISTCTRL0.LBISTREQ/LBISTREQRED: 这两个位域设置为1则触发LBIST

3) LBISTCTRL0.LBISTRES: 设置为1可以复位LBIST Controller, 复位之后, LBISTDONE会被清零, SIGNATURE值也会被清零

4) LBISTCTRL0.LBISTDONE: 用于表征LBIST Controller的执行状态, 0表示自从上次Power on Reset之后没有LBIST执行, 1表示至少有一次成功执行完了LBIST测试

03 LBIST的触发流程

LBIST检测支持两种触发方式, 一种是通过BMI配置触发, 一种是软件触发.

1) BMI触发

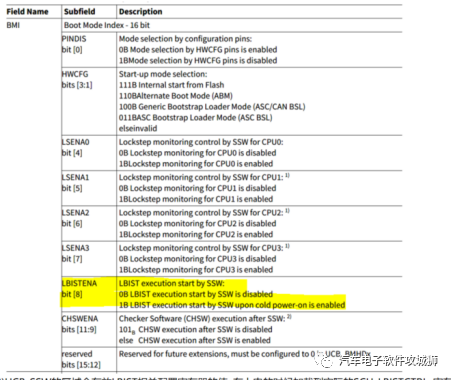

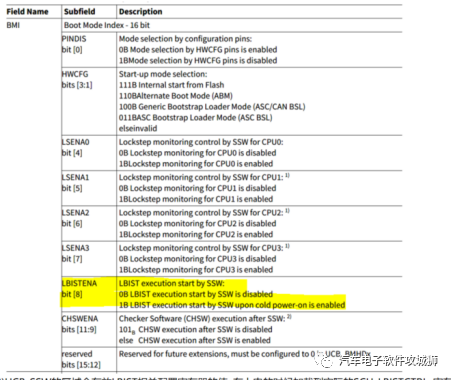

Aurix TC3xx在上电的时候会检测有效的BMHD, 其内部的BMI结构中包含了LBIST是否使能的信息, 如果LBISTENA位设置为1, 则TC3xx在SSW运行的过程中会触发LBIST自检. 否则不进行该 *** 作.如下图所示:

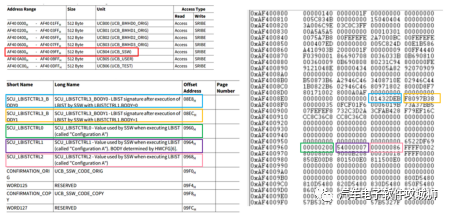

UCB_SSW的区域会存放LBIST相关配置寄存器的值, 在上电的时候加载到实际的SCU_LBISTCTRLx寄存器当中

值得注意的是, 其中SCU_LBISTCTRL1的第27bit, BODY位是由HWCFG6引脚的电平决定的

HWCFG6配置为低电平 ---- BODY = 1

HWCFG6配置为高电平 ---- BODY = 0

但是HWCFG6的电平不会影响UCB_SSW的结果, 而是直接锁存到真实的SCU_LBISTCTRL1当中.

下图是实测的UCB_SSW里面的LBIST相关寄存器的配置

可以看到它只支持ConfiguraTIon A的配置

针对ConfiguraTIon A的定义, 可以在各个芯片具体的Appendix UM里面找到, 以TC39x为例:

2) 软件触发

软件触发的概念, 是通过手动配置相关寄存器来实现LVIST的测试. 具体 *** 作步骤如下:

先将LBISTCTRL0寄存器的LBISTRES寄存器置1, 来复位LBIST Controller, 这时候LBIST相关的结果寄存器都会清除, 可以通过读取LBISTCTRL0.LBISTDONE是否为0判断

通过配置SCU_LBISTCTRL1来选择相应的BODY, SCU_LBISTCTRL2可以不配置, 采用默认值

配置SCU_LBISTCTRL0, 需要将LBISTREQRED和LBISTREQ bit都置1, 这样就会触发LBIST的测试

相关的代码实现如下图所示:

04 LBIST的执行与结果判定

当采用BMI触发LBIST或者软件触发LBIST测试之后, LBIST分别会在SSW和ApplicaTIon SW里面执行相应的LBIST测试. 对于Configuration A的LBIST测试, 其执行时间大概是6ms左右.如果测试过程中没有任何异常,则硬件会自动触发LBIST复位,Aurix的复位状态寄存器中的LBTERM位会被置1.

在用户代码中可以读到LBISTCTRL0的LBISTDONE位被置1,之后再checkLBISTCTRL3的SIGNATURE位,是否与预期的值相符,需要注意的是,不同的芯片(设置同一个芯片不同的step,其预期的签名值是不同的)。具体需要参考芯片的手册。

此外关于LBIST的功能安全机制,请参考Aurix的安全手册。

编辑:黄飞

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)