这次我们结合图示好好讲解一下逻辑电路中的几种常用部件。ps:这边的图随便看看就好,这个只是Logisim软件里的样子,不具有普适性。

首先是时钟。

逻辑电路里的时钟肯定不同于我们生活中所讲的时钟,但是有相似的特征。我们生活中的时钟告诉我们现在是几点,而逻辑电路中的时钟则告诉电路现在是什么周期,同时电子表使用的是逻辑电路中这种时钟来反映真实世界中的时间。看到上面的那一根短线了吗?现在是深绿色所以代表的是低电平0。一个完整周期有一个高电平和一个低电平,用x轴为时间y轴为电压的图像表示就是矩形波。周期越短,频率就越高,一般来讲电路的性能就会越好。一些热衷于折腾电脑硬件的玩家(比如我)会给硬件超频或降频,这里的超频或降频就是调整这个时钟频率。这里解释一下,硬件刚出厂的时候厂商对硬件频率的设定会相对保守。太高的频率会让设备运行出错,因为太快了……太慢的频率性能相对较差。并且每一个出厂硬件的体质不一样,有的可能可以稳定在很高的频率有的则可能很不稳定即使频率很低,这个与制造有关系。用户可以根据自己手中的硬件适当调整频率达到提高性能或降低功耗等目的。另外作为时钟,它的震荡需要很稳定,肯定不能忽快忽慢。我们使用石英晶体来解决这一问题。石英晶体两端接上交流电之后会产生异常稳定的震荡。具体原理在此不做深究,感兴趣的可以百度压电效应。

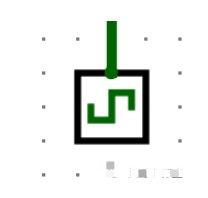

接着是D寄存器(D触发器,除此以外还有JK触发器、T触发器等)。

D寄存器一共有四个输入(最下面那个R输入可以不要),和一个输出。D输入现在要存入的数据。WE是写使能信号,WE信号为1则把D输入的值记住,WE信号为0则不记住D输入的值。三角标连接着是上文的时钟,每到低电平和高电平的交界处(上升沿或下降沿)时允许记忆一次。举个例子,该寄存器为上升沿寄存器。那么时钟信号为下降沿时该寄存器不记住任何数值,其存着上一次记住的内容。时钟信号为上升沿时但WE信号为0的时候,仍然不记住任何数值。当时钟信号为上升沿并且WE信号为1的时候才记住D输入的数值。一般D输入连接着数据通路,WE连接着控制通路,这是硬件电路的主要两大通路。Q输出寄存器中储存的数值,无论时钟怎么走,存储的数值不变,你总是能从Q中读到稳定的该数值。至于最下面的R输入,个人觉得用处不大,这个是用来强制清零的,无论这个寄存器现在是什么模样,只要R输入是1,那么就清零。

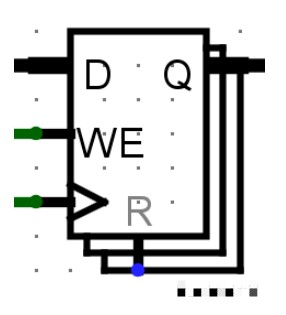

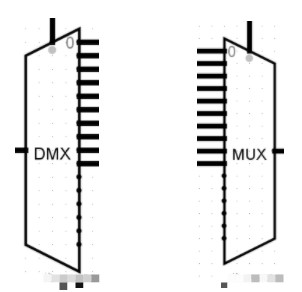

这两张图分别是选路器(DMX)和多路复用器(MUX)。DMX和MUX的左侧和上面的接口作为输入,右侧接口作为输出。他们的功能其实非常相似,DMX是将这左侧这一输入发送到右侧某个输出接口,MUX则是将左侧的某个输入发送到右侧这一输出接口。最上面的输入信号作为sel位(选择位)用来选择哪个作为输入或输出(sel位的位数决定了能有多少个输入或输出)。以DMX为例,左侧输入信号为1,sel位为0000时(此时一共有16个输出),右侧第一个输出为1,其余皆为0。再以MUX为例,假设左侧第一个输入为1其余皆为0,sel位为0000时,右侧输出为1。Sel位为非0000数的时候,右侧输出为0。

上文中的寄存器(触发器)、DMX和MUX皆是由与或非门构造而成。这里不再赘述,感兴趣的可以自行深入了解。此外常用的部件还有tunnel、RAM、ROM等,下次再一并讲解。

审核编辑:刘清

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)