一、技术简介

1.1名词解释

千兆网,又称吉比特以太网(Gigabit Ethernet)是一个描述各种以1G比特每秒速率进行以太网帧传输技术

千兆网的传输方式有多种,我们这篇笔记以1000BASE-T为例。1000BASE-T在IEEE 802.3ab中规定,该 标准于1999年通过,该标准将吉比特以太网定义为利用非屏蔽双绞线(Unshielded Twist Pair)五类线(Category 5)或六类线缆(Category 6)进行的数据传输,并被称作1000BASE-T。在 802.3ab 标准中,吉比特以太网成为一种可以利用现有的铜缆基础设施实行的技术。

1.2基本技术原理

1000BASE-T PHY 支持通过 4 对最低为 CAT5 的对称电缆进行全双工基带传输。1000Mb/s 通过四个线对, 每对 250Mb/s 的传输速率实现。使用混合器及消除器允许在同一时间在同一线对上传送和接收符号,可实现全双工传输。每个线对使用 125 MBd 调制率的基带信号。传送的符号从四维五级符号结构 (4DPAM5) 中选择。

二、技术细节

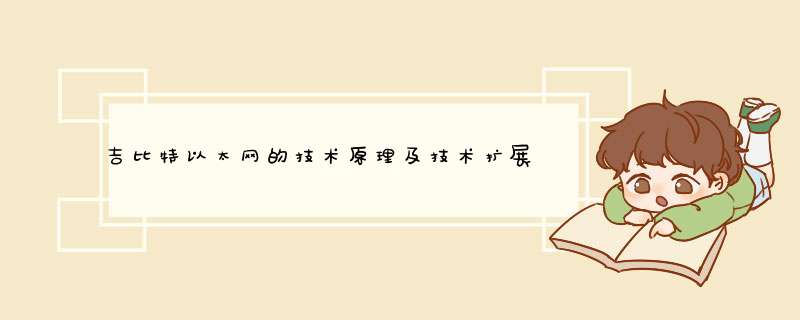

2.1 基本结构

基本结构分为MAC、PHY个MDI三部分,这个在前面都讲过。

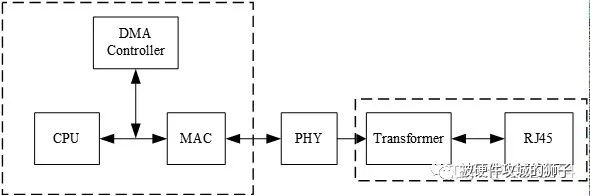

接下来我们看一下PHY部分的分层,下面这张图截取自IEEE 802.3ab

GMII:千兆网的媒体独立接口,用来和MAC进行通信。

PCS:物理编码子层,用来对数据进行编码(在发送数据时)和解码(当接收数据时)。在千兆网中用的8b/10b编码。

PMA:物理媒体连接子层,向PCS子层提供与媒体无关的方法,以支持使用面向串行比特的物理媒体。执行并串/串并转换。

PMD:物理媒体相关子层,定义物理层信令和媒体相关接口(MDI),以及所支持的媒体类型。在千兆网中最终产生的就是四个差分对类型的信号。

MDI:媒体相关接口,用来将PMD子层和物理层的线缆连接。在千兆网中就是四对差分对。

2.2 MAC 层接口

从 MAC 层接口到千兆 PHY, IEEE 802.3ab 标准中有三种不同的选择:标准介质独立接口 (MII) GMII、SGMII 或 RGMII。

2.2.1 GMII

GMII 的用途是使各种物理介质对 MAC 层透明。GMII 可接受GMII 或MII 数据、控制和状态信号,并分别将其路由到1000BASE-T、100BASE-TX 或10BASE-T 模块。

GMII 提供全双工 *** 作并且是8 位宽传输及接收数据通道接口,采用125 MHz 时钟,设定速度可达1000Mb/s。GMII 向后兼容MII 规范,从而支持 10 (2.5MHz) 及100 (25MHz) Mb/s 速率。数据和定界符与时钟基准同步。它同时提供简单的管理接口。具体信号定义如下:

发送器:

◇ GTXCLK——吉比特TX..信号的时钟信号(125MHz)

◇ TXCLK——10/100M信号时钟

◇ TXD[7..0]——被发送数据

◇ TXEN——发送器使能信号

◇ TXER——发送器错误(用于破坏一个数据包)

注:在千兆速率下,向PHY提供GTXCLK信号,TXD、TXEN、TXER信号与此时钟信号同步。否则,在10/100M速率下,PHY提供 TXCLK时钟信号,其它信号与此信号同步。其工作频率为25MHz(100M网络)或2.5MHz(10M网络)。

接收器:

◇ RXCLK——接收时钟信号(从收到的数据中提取,因此与GTXCLK无关联)

◇ RXD[7..0]——接收数据

◇ RXDV——接收数据有效指示

◇ RXER——接收数据出错指示

◇ COL——冲突检测(仅用于半双工状态)

GMII 使用总共最多 25 引脚。

2.2.2 RGMII

RGMII 旨在减少连接在MAC 与PHY 的引脚数(相对于GMII 的24 引脚,RGMII 只需12 引脚)。通过优化, RGMII 由 12 个信号组成:

6 个接收信号:RX_CTL、RX_CLK 和RX_D[3:0]

6 个发送信号:TX_CTL、TX_CLK 和TX_D[3:0]

相比于GMII,RGMII信号线减少了,时钟信号依然为125M,但是要保证1000M数据传输。为实现此目标,数据通道及所有相关控制信号都被减少并多路复用。时钟的上升沿与下降沿均使用。在千兆运行过程中,GTX_CLK 和RX_CLK 时钟为125MHz, 对于10 和100Mb/s 运行,时钟频率分别为2.5MHz 和25MHz。

2.2.3 SGMII

SGMII即Serial GMII,串行GMII,收发各一对差分信号线,时钟频率625MHz,在时钟信号的上升沿和下降沿均采样。因为SGMII使用了serdes技术,用到了8b/10b (SerDes) 编码。所以SGMII接口的速率依然是625M*2*8b/10b=1000M。SGMII接口抗干扰能力比较强,可以通过背板进行信号传输。

2.2.4 串行管理接口

串行管理接口SMI)由管理数据时钟MDC以及管理数据输入/输出(MDIO) 信号组成。它可以对PHY 的内部寄存器空间的状态信息及配置进行访问。当一个地址被用于识别相应 PHY 受控端,基于串行通信协议,MDC 以及MDIO 信号可以在几个PHY 之间共享。

2.3编码技术

PHY中的PCS层是物理编码子层,用来对MAC层通过GMII或者RGMII发送来的数据进行编码以便通过MDI传输,当然也同样承担着解码任务。编码完成的任务是保证高速的数据能正常通过线缆进行传输。

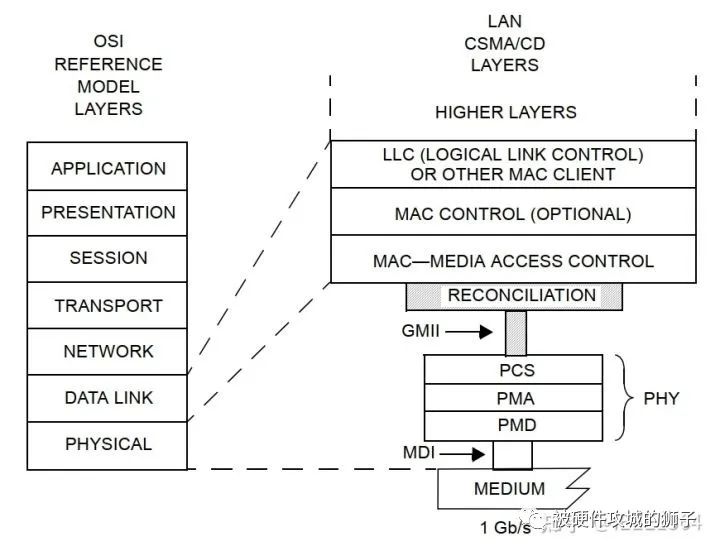

1000Base-T在PCS层使用4D-PAM5编码,所谓的PAM5表示每个码元有五个电平-2,-1,0,1,2,但是每个码元只能表示4个符号,00,01,10,11,因为还有一个电平表示前向纠错码FEC。所以一个码元能传输2bit信息(4=2^2)。这样做比我们平常的二电平编码提高了带宽利用率,并能把波特率和所需信号带宽减为原来的一半(125Mbps)。但多电平编码需要用多位A/D,D/A转换,采用更高的传输信噪比和更好的接收均衡性能。

PCS层其实将8bit数据转换成4个码元。数据在PMD层需要再做一个8b/10b编码,然后将数据放到4个差分对上进行传输,所以每个差分对上的码元速率为1000M/8*4/4=125M。所以,尽管是千兆速率,但实际上对示波器的带宽要求只需能高保真采集125MHz信号即可。

所以在差分信号对上我们测试到的眼图应该是下面这样的。五个电平四只眼,周期是8ns。

2.4 MDI接口

1000BASE-T MDI接口的拓扑结构如下

其信号号线定义如下:

通常我们使用的水晶头引脚顺序定义如下图:

差分对要求阻抗为100欧姆,信号摆幅在不同速率下受下面表格参数约束(参考DP83867IR数据手册)

在MDI接口中我们需要使用变压器耦合,因为IEEE 802.3 规定, 带 MDI(非电源接口 (PI)) 的 PHY 应该在端口设备电路之间提供电隔离,包括机架接地(如果存在) 以及全部 MDI 引线。电隔离应当承受至少以下一种电气强度测试:

• 1500 VRMS, 在 50 至 60Hz 之间 60s

• 2250-V 直流 60s

• 十个 2400V 极性交替脉冲构成的脉冲序列,应用间隔不小于1s

为满足此要求, 通常使用变压器隔离。1000BASE-T 的典型变压器配置可通过下图的一个差分对来反映。

根据 PHY 设备,每个MDI 差分信号对都可能都需要并联端接电阻。端接阻抗通常为100Ω 。有些PHY器件(如 DP83867IR)含有集成端接电阻,因此不再需要外部端接电阻。下图是DP83867IR的MDI接口的原理图

说明:

1.上图中TPD4E05U06DQA 为TVS二级管。

2.在 MDI 连接中使用的变压器提供本地电路与网络线缆的直流隔离。在隔离绕组的中间抽头处有一个“BobSmith”端接, 通过一个 75Ω 和一个 1000pF 的电容器接地。端接电容的额定电压应当至少为 2kV。BobSmith 端接降低了共模电流流过产生的噪声。

3.需要考虑从 RJ45 到磁场及从磁场到 DP8867IR 的走线长度, 因为这些信号是差分对信号。这意味着信号要尽可能在满足走线长度要求的情况下长度差异尽可能大。为确保数据完整性, 走线差异应当小于 10mil(0.254 mm)。

2.5 技术优势说明

千兆以太网使用4对差分对进行信号传输,在信号传输和设计复杂度之间取得很好的平衡。其实因为后面的万兆网方案设计提供基础和思路。

三、技术扩展

1.千兆网技术标准

2.千兆网的EMC设计和测试

千兆的EMC设计是比较有挑战的,参考资料里面的《符合 EMI/EMC 标准的工业温度级双端口千兆位以太网参考设计》是一篇非常有实践意义的文章。这篇文章给出了完整的参考设计,还对EMC测试进行了详细的表述,对于没有做个深入EMC测试的同仁来说是非常好的学习资。可以从中学习EMC测试的方法。

参考资料

1.1. IEEE Std 802.3-2008, IEEE

ieee802.org/3/index.htm

2.DP83867IR, TI

TI.com.cn/product/cn/DP

3.以太网物理层信号测试与分析,eefocus,佚名

eefocus.com/communicaTI

4.符合 EMI/EMC 标准的工业温度级双端口千兆位以太网参考设计 ,TI

ti.com.cn/cn/lit/ug/zhc

-----------------------------------------------------------------------------------

扩展:SERDES与SGMII

SERDES的概念:

SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。它是一种主流的时分多路复用(TDM)、点对点(P2P)的串行通信技术。即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。这种点对点的串行通信技术充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,从而大大降低通信成本。

这是一种通信技术的统称。

SERializer/DESerializer

Translates an n-bit parallel bus into adifferential serial stream

Receives a differential serial stream andconverts it back to an n-bit parallel bus

SerDes technology simplifies transferringthe parallel data by eliminating the skew between the parallel data paths andreduces system cost by narrowing the data path.

SGMII的概念:

如果说到SGMII则会想到MII、GMII、XGMII、QGMII等信号接口。

SGMII--Serial Gigabit Media IndependentInterface SGMII是PHY与MAC之间的接口,类似与GMII和RGMII,只不过GMII和RGMII都是并行的,而且需要随路时钟,PCB布线相对麻烦,而且不适应背板应用。而SGMII是串行的,不需要提供另外的时钟,MAC和PHY都需要CDR去恢复时钟。另外SGMII是有8B/10b编码的,速率是1.25。所以,SGMII需要PHY来做8b/10b的解码工作。

SGMII在物理上是兼容SERDES信号的,所以走的通道也是SERDESlane。

实例1:

在intel的LAN芯片中,一般情况都是MAC和PHY在一起的。所以通过eeprom可以配置LAN芯片输出信号的种类。可以接电口RJ45和光口SFP。

如果我们需要直接从LAN芯片中接SFP接口,则需要配置成SerDes(1000Base-BX)mode;

如果接RJ45,则需要在flash中配置成copper PHY。

如果需要接另外一颗PHY,则需要在flash中配置成SGMII Mode,送如PHY中。

实例2:

在octeon的芯片中QLM可以配置成SGMII和1000BASE-x。这两种模式走的通道均为SERDES lane。如果接电口RJ45,则需要配置成SGMII,通过PHY来完成解码和negotiation。

如果接光口SFP,则需要配置成1000BASE-x,让QLM切换成PHY来实现negotiation和解码动作。这样可以不用接PHY。

10/100/1000:数字 100 用单位 MHz (Megahertz) 表示网线设计的频率。即 100MHz。MHz 的值越大,网线所支持的速度就越快。如果你尝试将这种类型的网线用于更高的频率(和速度)中,那么它将不工作或者变得极为不可靠。100 MHz 以每秒 100Mbit 的速度传输,这在理论上指的就是12Mbps。然而,在实际中,可能还无法获得超过 4Mbps。

BASE:BASE 是英文 baseband 的缩写,指的就是基带。表示没有使用频分复用或者其它频率转换技术,每一个信号在一个单一频率上完全控制线缆。

数字T/F/C等:一般数组表示传输长度;T 代表承载信号的物理介质是双绞线缆(分为UTP(Unshielded Twisted Pair,非屏蔽双绞线)和STP(Shielded Twicted Pair,屏蔽双绞线)),在这里每一对传送信号的双绞线互相缠绕以 (FEXT 和 NEXT 之间) 减少电磁干扰和串扰;F 表示光纤

最后的字母或数字(4/X等):在同一种传送速率下有多种不同的标准,它们之间以一个字母或数字跟随 T/F/C 之后的方式来区隔(例如 TX)。它显示了网线的结构并指出包含的绞线对的数量。某些高速标准使用同轴电缆,则分配代号为 CX。

编辑:黄飞

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)