印度科学研究所 (IISC) 的研究人员为了重新激发对模拟芯片设计的需求,描述了未来模拟 AI 芯片的框架。

随着行业继续推动机器学习 (ML)和人工智能 (AI)的低功耗和高性能处理,大量新概念和技术已成为中心舞台。其中,模拟计算作为一种更有效处理的令人兴奋的方法已经复兴。

尽管如此,该技术对于这个给定的应用来说还是相对较新的,并且还有很大的改进空间。本周,IISC 的研究人员发表了一篇新论文,描述了可扩展模拟 AI 芯片未来的新框架。

IISC 的 ARYABHAT-1 芯片。图片由 NeuRonICS Lab、DESE、IISc提供

本文将讨论模拟计算对 AI 的好处、该技术面临的一些挑战以及 IISC 的新研究。

为什么要转向模拟?

模拟计算是一种早于数字计算的技术,但随着数字计算的兴起,它在很大程度上被遗忘了。现在,研究人员再次将目光投向了模拟,这一次它似乎在几个方面被数字打败了。

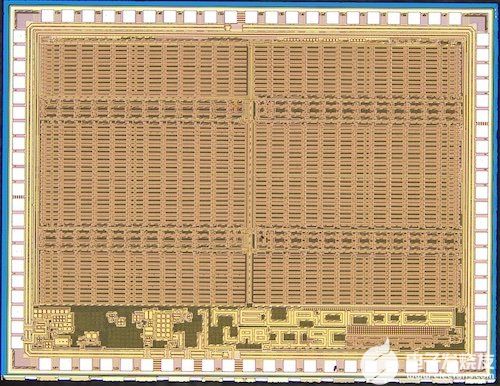

传统的冯诺依曼架构受到数据移动的限制。图片由IBM提供

随着数据速率越来越快、处理节点越来越小、全球互连越来越长,行业的一个新兴趋势是数据移动能量的重大影响。

越来越多的寄生效应导致数据进出内存的物理移动已成为影响整体芯片功耗的最重要因素之一。再加上机器学习,一个数据非常密集的应用程序,我们发现冯诺依曼架构不再适合人工智能/机器学习。

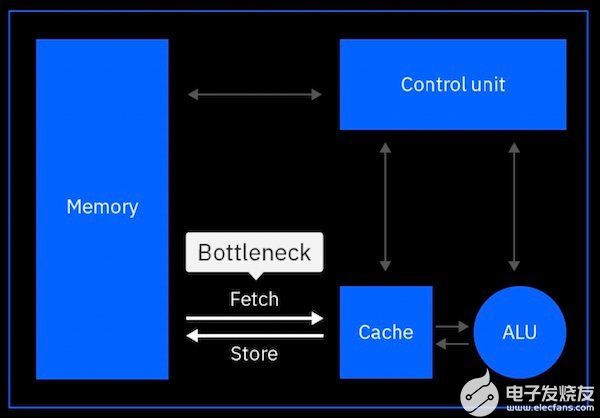

模拟 AI 将处理直接带到内存中。图片由IBM提供

相反,模拟计算允许内存计算,数据可以在存储的地方进行处理。主要好处是整体数据移动显着减少,从而降低了整体能源消耗。

这样一来,与用于 AI/ML 应用的传统数字电子产品相比,模拟 AI 可以提供高达 100 倍的能效提升。

模拟 AI 扩展的挑战

尽管具有效率优势,但模拟计算在成为数字计算的合法竞争对手之前仍面临若干挑战。

为 AI/ML 设计模拟计算的关键挑战之一是,与数字芯片不同,模拟处理器的测试和协同设计很困难。传统上,VLSI(超大规模集成)设计可能包含数百万个晶体管,但工程师可以通过编译高级代码来综合设计。此功能允许相同的设计轻松移植到不同的工艺节点和技术世代。

跨导 (gm/Id) 作为不同工艺节点处 (Vgs–Vth) 的函数。该图显示了轻松扩展模拟设计所面临的挑战。图片由Kumar 等人提供

然而,由于晶体管偏置机制、温度变化和有限的动态范围的差异,模拟芯片不能轻易扩展。结果是每一个新的世代和流程节点都需要单独定制和重新设计。这一结果不仅使设计更加耗时和昂贵,而且还降低了可扩展性,因为向新一代技术的过渡需要更多的手动工作。

要使模拟 AI 成为主流,首先需要解决设计和可扩展性方面的挑战。

IISC 扩展 AI 的框架

为了解决这个问题,IISC 的研究人员在他们最近发表的论文中提出了一种用于可扩展模拟计算设计的新框架。

他们工作的关键概念围绕边际传播 (MP) 的泛化展开,这是一种数学工具,以前在使用 MP 原理 合成模拟分段线性计算电路中显示出价值。

出于这种概括,研究人员开发了一种新颖的基于形状的模拟计算 (S-AC) 框架,该框架允许研究人员近似 ML 架构中常用的不同功能。

基于所提议的模拟框架构建的芯片的测试设置。图片由NeuRonICS Lab、DESE、IISc提供

结果是一个框架可以成功地在精度与速度和功率之间进行权衡,例如数字设计,并且还可以跨不同的工艺节点和偏置机制进行扩展。

作为概念验证,研究人员实施了许多 S-AC 电路,以在几个不同的过程中表示 ML 中的常见数学函数。在此过程中,研究人员成功地使用电路仿真来证明电路 I/O 特性在计划的 180 nm CMOS 工艺和 7 nm FinFET 工艺中保持合理相同。

借助新框架,研究人员希望能够在不久的将来创造出能够实现更具可扩展性和成本效益的模拟 AI 设计。

审核编辑 黄昊宇

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)