关于Buck和Boost的,我已经写了几篇,不过很少提到PCB Layout,这篇就说说PCB Layout。

很多DCDC芯片的手册都有对应的PCB Layout设计要求,有些还会提供一些Layout示意图,都是大同小异的。

比如我随便列几点buck的设计要点:

1、输入电容器和二极管在与IC相同的面,尽可能在IC最近处。

2、电感靠近芯片的SW,输出电容靠近电感放置。

3、反馈回路远离电感,SW和二极管等噪声源。

那你知道这些要点都是怎么来的吗?

如果拿到一个具体的芯片,因为芯片管脚分布的问题,可能这些条件不能同时满足,那什么办?到底孰轻孰重?

举个Buck的例子

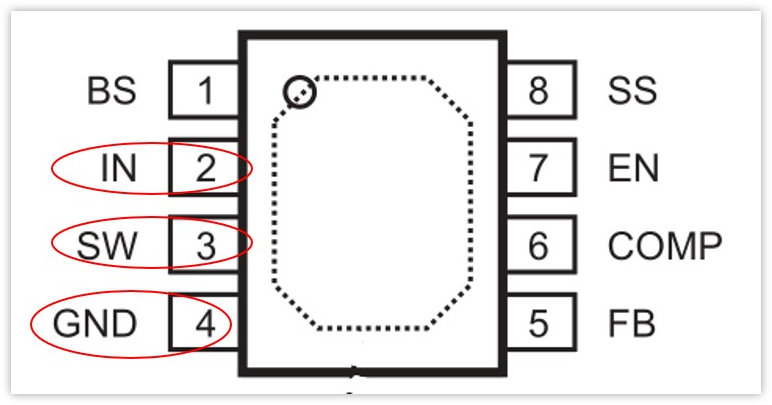

比如下面这个buck,它的管脚分布就不好。

SW在IN和GND之间,如果按照要点,直接将输入滤波电容放到IN和GND旁边,那么SW的信号就出不来,而电感也要求放在芯片旁边,这就矛盾了。

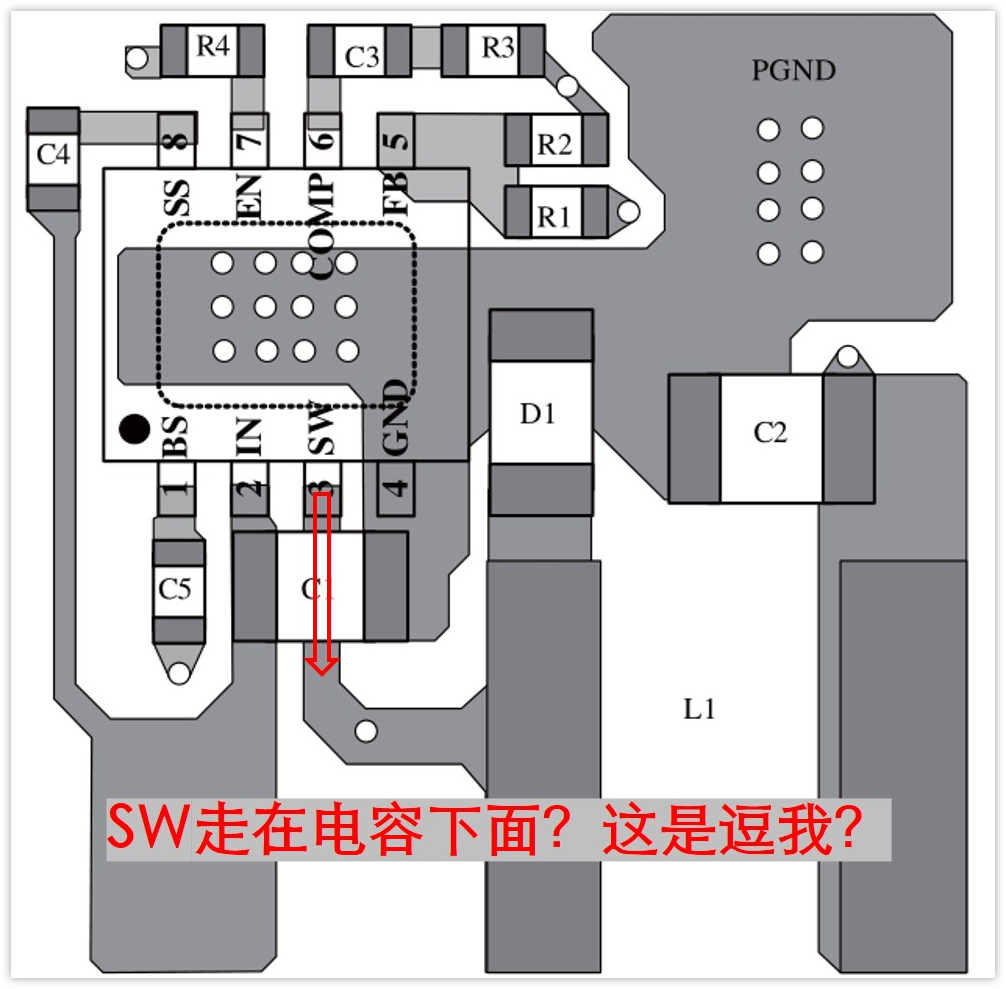

那我们看看这个芯片手册推荐的Layout

芯片手册推荐的layout倒是都就近放置了,但是它的方法是SW在输入滤波电容底下走线,这是逗我吗?这在现实中能做到?

我们不能采用芯片手册推荐的这种方式,但事实是这种管脚分布的芯片多得是,那我们的Layout如何布局布线呢?

这个问题先不回答,我给大家说一个最根本的方法:

DCDC的Layout终极奥义——心中有环

心中有环

“环”,指的是有大电流流过的闭合回路。我们只要控制好这个环,Layout基本就成功一大半了。

下面来看为什么

以BUCK为例,BUCK电路存在两个状态,上管导通和下管(或者是二极管)导通,因此存在两个大的电流环路。

知道这两个环路有什么用呢?

我们要让这两个环路的面积越小越好,因为每一个电流环都可以看成是一个环路天线,会产生辐射,会引起EMI问题,也会干扰板上其它的电路,而辐射的大小与环路面积呈正比。

电流环所生成的高频磁场会在离开环路大约 0.16λ 以后逐渐转换为电磁场,由此形成的场强大约为:

可以看到,辐射的大小与环路的面积,频率的平方,电流的大小呈正比。

那我们是不是让这两个环路面积最小就可以了呢?

确实是的,不过我认为了解这点还不够,突出不了重点。

从拓扑图可以看出,这两个环路有公共的部分,一个环路包含另外一个环路,这导致那个大的环路的电流各个器件节点可能不一样,所以不好用那个公式计算。

所以,我们需要变通下,怎么变通呢?

辐射产生的原因,就是因为电流产生了磁场,电流是变化的,所以磁场也是变化的。电流环围绕的面积里面的磁通量会随电流动态变化而变化,磁场生电场,电场生磁场形成了电磁波。

我们把那个大的电流环拆解为2个部分,如下图:

整个大的环可以看成由输入环路和输出环路叠加。

可能有点难以理解,因为输入环路根本就不是个实际的电流回路,它是本身存在的两个电流环路的差值。

这其实只是个等效的方法而已,我们的目标是要知道总的大的回路里面的磁通量变化情况,这样等效之后就可以求了,我们可以分别求得输入环路和输出环路的磁通量情况。

输入环路的等效电流就是输入电容Cin的电流

输出环路的电路等效电流就是电感的电流

它们都是只看交流,直流分量不管,直流的频率看成是0Hz,不会辐射电磁波。

之前我们的《手撕Buck!Buck公式推导过程》已经分析了,输入环路电流(Cin)和输出环路电流(电感)分别如下:

可以看到,在开关切换的时候,输入环路的电流是会突变的,也就是会有很大的di/dt,那么输入环路的磁通量也是突变的(准确的说是变化速度很快),存在很多的高次谐波。

从前面的公式我们知道,辐射强度与频率成正比,因此这些高次谐波更容易被辐射出去。

输出环路的电流是三角波,是没有突变的,所以高次谐波辐射强度要小些。

信号强度对比

这里可能有人会说了,三角波的频谱理论不也是无限的吗?也有很多高频分量啊,怎么辐射就小一些。

确实,三角波的频谱是无限的,不过频率越高,幅度会越低的,也就是说高频分量能量少,那么辐射也就少了。

关于这一点呢,我们简单做个仿真,看下电流的傅里叶变换fft就知道了。

使用LTspice软件仿真,5V转1.8V的buck电路图如下:

输入环路电流(输入电容电流)和输出环路电流(电感电流波形)如下:

有了波形,我们看下fft(仿真软件很容易做到),看下频谱:

可以看到,基频就是BUCK芯片LTC3307A的开关频率2Mhz,2Mhz两者的强度相差不是很大,就2-3个db左右,但是在10Mhz的时候,就已经相差20db了,频率越高,差得越多。

也就是说,输入环路的高频谐波能量要比输出环路大得多,如果有经验的话,应该会知道,引起EMI超标的一般也就是高频超标,所以因为输入环路造成EMI的可能性更高。

我这里费了一些功夫,其实就是为了说明:

BUCK的输入环路非常非常重要,环路面积一定一定要小。

另外一点需要注意,是环路面积小,不是走线短,这两者还是有区别的。有时走线短并不一定环路就小,我们的目标是环路的面积,而不是长度。

我们布局走线尽量走成扁的那种形状。

我们回到开头的那个DCDC芯片,输入环路指的什么呢?

显然,这个芯片的开关管在芯片内部,所以输入环路就是芯片的IN管脚,与GND管脚,以及输入滤波电容形成的环路,那么除了芯片之外,器件就只有输入滤波电容了。

所以最理想的layout就直接将输入滤波电容跨接到芯片的IN脚和GND管脚,从这一点上看,芯片手册推荐的layout与这一点是符合的,只是这样做了之后,SW出不来而已。

这颗dcdc芯片给出的推荐layout确实是保证了输入环路最小。只不过它将SW信号走在了输入滤波电容下面,这个实际电路通常是行不通的,因为电容下面根本就走不了比较宽的线的。

那咋办呢?

我估计会有人认为将输入滤波电容放置到PCB的背面,在Vin和GND管脚正下方放置滤波电容,通过过孔接过去,这样看起来环路也比较小。

我的看法是,如果有其它更好的方式,那就不要这么做。

因为过孔会存在寄生电感,加了过孔会增加这个环路的电感,导致发生LC振荡。直接的现象就是在SW处产生高振铃,这个高振铃意味着这个环路中,谐振频率的信号分量很强。

也就是说尽管环路面积不大,天线效应不强,但是我的信号强度变大了呀,辐射不一定差。

关于振铃,以前专门写过《BUCK的振铃实验与分析》,可以去看一看。

曾经的教训

多年前,我曾经就遇到一个电源芯片的输入滤波电容放背面,通过过孔连接,结果搞得整个板子的噪声很大,而将滤波电容直接手动跨到Vin和GND上面,立马问题就没了。

当时我还不懂,觉得不可思议,打孔的数量并不少,滤波电容也是在底部就近放置的,居然还有问题,几个孔威力这么大?

后来还专门改板解决,直接将输入滤波电容与芯片同层,并在表层连接,问题就解决了。 上面说了这么多,其实主要说的就是,BUCK电路,输入滤波电容的布局布线非常重要,是重中之重,是第一要考虑的。

如果是异步Buck,那么就有一个外置的二极管,这个二极管构成了输入回路的一部分,那么它的位置,与输入滤波电容的重要性是同级别的,要放得离芯片的SW比较近,具体怎么摆,咱们看回路面积怎么小就知道了。

输出环路

前面写了一堆,一直在强调输入环路,那输出环路不重要吗?

当然不是,其实从前面的fft也能看到,输出环路也有高频分量,所以输出环路也要越小越好,只是它相对输入环路来说高频分量强度不高,在二者布局有矛盾的时候,当然是优先考虑输入环路。 我怎么画

总而言之,如果是我,我会将开头提到的BUCK这样Layout:

Boost情况如何?

上面这是buck的一个情况,那么boost是怎么样的呢?

输入回路是最重要的吗?优先需要考虑的是输入滤波电容吗?

答案是NO Boost也有两个环,是下图这样的

跟buck一样,我们把它们分为两个部分,输入环路和输出环路,可以看到,输出环路是上面两个环路的差值。

与buck不同的是,电感在输入环路,其电流波形是三脚波,而输出环路的电流就是二极管的电流,是有突变的。

之前《手撕Boost!Boost公式推导及实验验证》也已经全面分析了这两个电流,波形如下:

也就是说,boost最重要的是输出回路,类似于Buck的输入回路。我们需要首先保障的是boost的输出环路尽量小。

具体实例就不举了。 Layout其它方面注意事项

除了大的电流回路,还有FB,补偿电路这些,是小信号电路,所以他们要尽量远离前面大的电流回路,远离电感等。

比如下面,就是左边比右边的好:

另外需要注意,关于大的电流回路,我们要把GND地看进去,不要用这些走线分割了大电流的回流地GND路径。

所以,你有的时候会看到,底层FB走线并不是最短的,而是绕了一下。

小结

总的来说,DCDC的layout,我们要做到心中要有电流环。

画板的时候,心里念叨一下,开关断开,电流咋咋咋流,开关导通,电流咋咋咋流。然后找到电流突变的那个环,那就是最重要的,得优先处理。

这个原则,其实不仅仅适用于dcdc,其它类型的电源,或者是大功率电路,都是如此的。

了解了这个原则,其实很多电路,都不用去细看芯片手册的pcb layout的注意事项了,它说的也就是这些东西,只不过是具体的措施而已。

这种将关键环路做到最小,算是从根源上杜绝问题的产生,远比后期想不改板,然后七搞八搞要强。

审核编辑:汤梓红

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)