关键词:可编程逻辑器件,周期信号测试仪,ISP芯片,自顶向下

1 引 言

周期信号测试仪是直接用十进制数字来显示被测信号周期的一种测量装置,它可以测量正弦波、矩形波、三角波等信号的周期。传统的设计是采用标准逻辑器件(如TTL74系列、CMOS4000系列),再由这些器件和其他元件自上而下组成数字系统,所用的元器件数量较多、体积大、功耗高、且可靠性差。本文采用现今流行的自顶向下(Top-Down)的设计方法,设计中选用LatTIce公司生产的在系统可编程器件ispLSI1016,以周期信号测试仪电路系统的开发设计为例,说明在系统可编程逻辑器件实现数字系统的具体方法。

2 周期信号测试仪的工作原理及设计方案

2.1 工作原理

周期信号测试仪的基本原理是在被测信号的一个完整周期内,对标准时钟脉冲进行计数。考虑到测试的准确性,被测信号的周期应远大于标准时钟脉冲的周期。假设标准时钟脉冲周期为1μs,则计数器在被测信号的一个周期内的计数值,就是被测信号的周期,单位为1μs。

2.2 测试仪的原理框图

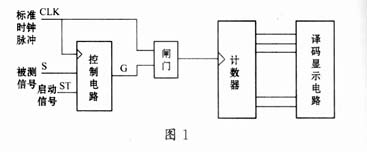

周期信号测试仪的原理框图如图1所示。测试仪主要由五位十进制计数器、闸门控制电路和译码

显示电路等组成。图1中,S为被测信号,ST为启动信号,CLK为标准时钟脉冲。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)