关键词:FPGA,Verilog HDL,层次设计方法,直接地址 *** 作

1 引 言

FPGA(现场可编程门阵列)的出现,改变了数字系统设计方法、增强了设计的灵活性,同时,在基于芯片的设计中可以减少芯片数量,缩小系统体积,降低能源消耗,提高系统的性能指标和可靠性,在实时监控方面有广泛的应用。

ISD语音芯片采用DAST(直接模拟存储技术),直接存储模拟信号,因而减少了失真,提高了录、放音质量,本文所用的ISD2560系列具有抗断电、音质好、使用方便、录放时间长等优点。然而,在产品应用中,大多数系统只利用了ISD芯片提供的无需地址的工作模式(共有6种),这些 *** 作模式实时性差、地址控制精度不高、 *** 作不灵活。本文从另一个角度论述了基于FPGA的ISD语音芯片的设计开发。

2 ISD语音芯片

ISD语音芯片目前有ISD1000、ISD1100、ISD1200/1400、ISD2500、ISD3340和ISD4000系列,本设计采用的是2500系列中的ISD2560芯片。ISD2560具有10个地址输入端,寻址能力可达1024位,前600个地址用于直接存取语音,地址600~767未使用,地址768~1024为工作模式选择用,因此最多能分600段;设有OVF(溢出)端,便于多个器件级联;单片存储时间为60秒,直接存储模拟语音信号。

ISD芯片的地址以信息段为基本组成单元,只要在分段录、放音 *** 作前(不少于300ns),给地址A0~A9赋值,录音及放音功能均会从设定的起始地址开始,录音结束由停止键 *** 作决定,芯片内部自动在该段的结束位置插入结束标志(EOM);而放音时芯片遇到EOM标志即自动停止放音。

3 硬件构成及实现方案

利用FPGA的可编程特性实现对ISD2560芯片的直接地址 *** 作,从而实现按地址位录音、放音的功能,提高芯片存储空间的利用率,并能自由选择存储地址;本文选择XILINX(全球最大的可编程器件供应商)的Spartan XL系列芯片,利用VerilogHDL语言编程设计,采用层次设计方法实现。

Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

3.1 设计思路

ISD2560芯片存储时间是60秒,内部有480K字节的EPROM存储单元,划分为600个地址单元,可以算出对于每一个地址单元的存储空间是480K÷600=800字节,对应的录放时间是100ms;同时,ISD2560内部的地址位从0~599对应这600个地址单元,其它地址位则在 *** 作模式或按键模式中使用。可见,芯片内部上下段之间在存储空间上不 连续,但在地址上具有连续性。所以,ISD芯片内部的地址可采用定时计数器的方法获得,并可采用直接地址法提取此地址段,实现实时控制、自由存储。3.2 系统总体结构设计(顶层设计)

基于FPGA的ISD2560语音芯片的设计开发主要完成两个功能:(1)触发或停止FPGA内部定时计数器计数,并将计数结果存入FPGA的内部存储器中;(2)利用直接地址法,提取用于ISD芯片录、放音所需地址。

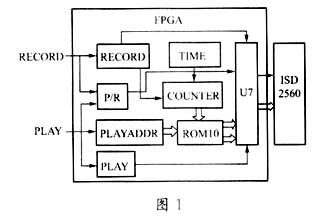

本系统是基于XILINX FOUNDATION 3.0平台开发的,其框图如图1所示,其中:

RECORD模块用于处理录音和停止录音的 *** 作,产生触发或停止定时计数器的信号以及录音时片选信号;

TIME模块利用FPGA的内部时钟模块最高频率产生频率为10Hz的信号作为计数器的时钟;为了提高系统的精确性,也可以通过外加时钟的办法实现。

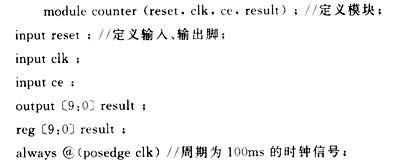

COUNTER模块为定时计数器,它利用周期为100ms的时钟脉冲,根据录音长短算出ISD芯片地址位,并发送到存储器,其Verilog HDL语言编程实现如下:

P/R模块产生整个电路录、放音的选择信号;PLAYADDR模块完成放音地址的产生;

PLAY模块将在放音时产生一个由高到低的脉冲作为片选信号;

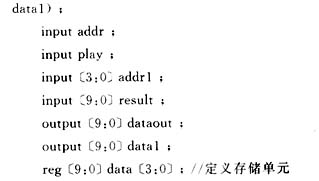

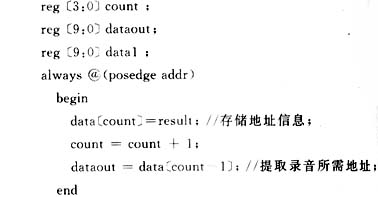

ROM10模块完成了存储器的功能,存储10位ISD芯片地址,并按照PLAYADDR产生的地址直接提取ISD芯片地址,其Verilog HDL语言编程实现如下:

module roml (addr,play,addrl,result,dataout,

U7模块由P/R模块的输出信号来选择输出。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)