摘要

在过去的几年中,纳米压印光刻引起了越来越多的兴趣。事实上,似乎有越来越多的潜在纳米压印应用和基本纳米压印光刻概念的变化。不同的纳米压印变体对于特定的最终用途应用各有优缺点,总体赢家和输家仍有待分选。德克萨斯大学 (UT)-AusTIn 于 1998 年开发了其版本的纳米压印、步进和闪光压印 (SFIL)。光固化液体以分步重复、逐个芯片的方式,而不是热辅助成型的全聚合物涂层晶片。SFIL 从一开始就专门针对半导体制造应用。在这些应用中,SFIL 具有作为室温、低压印力方法的优势。因此,SFIL 可以实现多级半导体器件制造所需的精细对准和覆盖控制。2001 年,SFIL 概念获得了 Molecular Imprints, Inc. (MII) 的商业开发许可,该公司成立的目的是开发具有 SFIL 功能的工具和相关流程。

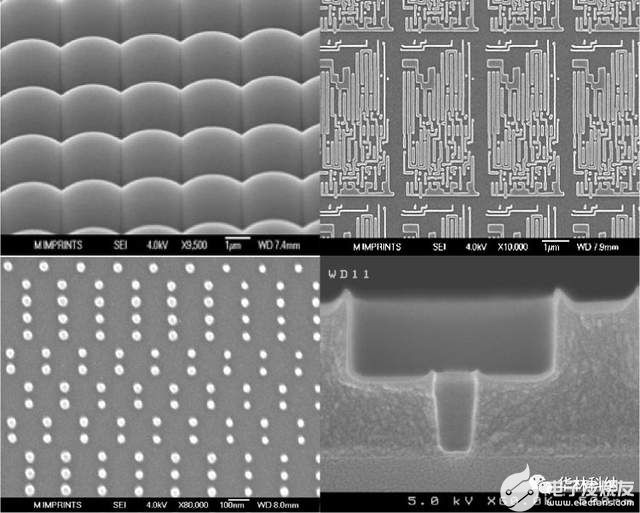

图 1. SFIL 压印结果显示为 (a) 密堆积微透镜,2 微米正方形;(b) 包含 30 纳米线和间距的 45 纳米节点逻辑芯片图案;(c) 32nm节点内存芯片触点,41nm半间距;(d) 具有 100nm 直径通孔的横截面、多层压印绝缘体。图片 1(a-c) 由 Molecular Imprints, Inc. 提供。

介绍

自 UT-AusTIn 最初开发以来的八年里,SFIL 工具已经变得非常复杂。最初的 UT 工具具有零重叠/对准功能,仅处理手动加载的 125 毫米晶圆,并且需要几分钟才能执行一次压印。现在 MII 的最新工具可以实现亚 10nm、3σ 对准。最新一代 SFIL 工具的吞吐量接近每小时 5 个 200 毫米晶圆。当然,单个工具的成本比光步进器低得多,而且每代工具的生产量都在提高。但在许多新兴应用中,可能不需要类似光步进器的吞吐量。

实验

虽然在短期内将 SFIL 用于半导体的栅极或接触层的大批量制造是不可行的,但 SFIL 是目前可用于 32nm 节点小批量原型设计的少数方法之一。另一个引起半导体社区兴趣的 SFIL 应用是使用多层模板直接、同时压印多个器件级别:见图 1(d).4, 5 SFIL 可以将布线和通孔级别打印到低-k 介电材料在单个压印光刻步骤中,从而将与后端 (BEOL) 处理相关的步骤数量减少 2 倍或更多。

发展

半导体行业有非常严格的要求,并且对光刻技术有着根深蒂固的偏见。这种偏好使得一些人很难认真考虑任何非照片下一代光刻方法。然而,SFIL 在成本和分辨率方面的潜在优势是显着的。此外,纳米图案的新市场正在迅速出现,许多非半导体应用将需要非常高分辨率的图案,而这基本上只能从纳米压印中获得,因为这些新兴行业中很少有能够证明花费 5000 万到 1 亿美元购买一个先进的技术是合理的。光刻或 EUV 图案化工具。

审核编辑:汤梓红

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)