关键字:噪声检测;PCI总线;PCI 9052;WDM

前言

噪声检测系统用于对环境噪声进行样本采集和频谱分析,确定噪声中的频率分量是否对人体造成伤害。该系统分为高速数据采集卡和频谱分析两部分。数据采集卡将采样采集到的数据送入计算机内,由应用程序完成快速频谱分析功能。由于环境噪声是实时变化的,因此需要采集电路的高速采样和数据的高速传输。鉴于传统总线无法满足高速传输的要求,采用了PCI总线作为噪声检测系统的底层平台。

PCI总线是Intel公司推出的一种微机扩展槽接口标准,时钟频率为0~33MHz,其最大数据传输速率为132~264Mbps,有效克服了传统总线进行高速数据传输时的瓶颈现象,使数据的实时高速采集和传输成为可能。

数据采集卡结构说明

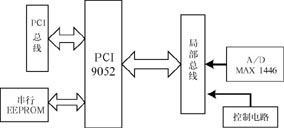

数据采集卡具有高速和速率可调节的特点。其前端采用声波传感器采集模拟噪声信号,采集到的模拟信号经过A/D变换器转换为数字信号,数字信号再经PCI总线传输到计算机内。该数据采集卡主要包括数据采集电路、PCI接口电路和逻辑控制电路三部分,采集卡结构如图1所示。下面分别介绍各个部分的功能。

1. 数据采集电路

数据采集电路是由声波传感器和A/D变换器组成的,传感器将采集到的噪声信号送入A/D变换器,转换成数字信号 输出。A/D变换器采用的是MAXIM公司的MAX 1446。MAX 1446有一路模拟信号输入,10位数字信号输出,工作频率可达60MHz。实际的数据转换时间为:转换时间+各种延迟=5+0.5=5.5个时钟周期,由此可知MAX 1446的转换时间最低可达0.1μs,即采样速率可达到100Mbps,为高速数据采集提供了最基本的硬件条件。

输出。A/D变换器采用的是MAXIM公司的MAX 1446。MAX 1446有一路模拟信号输入,10位数字信号输出,工作频率可达60MHz。实际的数据转换时间为:转换时间+各种延迟=5+0.5=5.5个时钟周期,由此可知MAX 1446的转换时间最低可达0.1μs,即采样速率可达到100Mbps,为高速数据采集提供了最基本的硬件条件。

2. PCI接口电路

考虑到PCI总线规范的复杂性,本设计采用了PLX公司的PCI 9052作为PCI总线接口芯片,以简化硬件设计。PCI 9052是作为PCI总线和局部总线一端的设备的桥梁,保证了局部总线一端的设备在符合PCI总线的规范后连接到PCI总线上。PCI 9052提供了多个内部寄存器,以尽量提高总线接口设计的灵活性和传输速率。所有的寄存器可分为PCI总线配置寄存器和局部总线配置寄存器两类。PCI总线配置寄存器是为符合PCI规范所设置的,局部总线配置寄存器用于设定局部总线的工作方式。

对于PCI 9052,需要一个EEPROM存储配置信息,当主机启动时,EEPROM完成对PCI 9052内部的PCI总线配置寄存器和局部总线配置寄存器的初始化。在设计中采用Microchip公司93LC46作为EEPROM存储配置信息。

3. 逻辑控制电路

逻辑控制电路的作用是用于产生目标设备准备好信号LRDYi#。在MAX 1446完成一个A/D转换后,使目标设备准备好信号LRDYi#有效,表明数据已经在数据线上,通知主设备可以从数据线上读取数据了。

由于MAX 1446的数据转换时间需要5.5个时钟周期,因此采用一个模6计数器作为控制电路,以保证在数据转换完成后,才产生LRDYi#。

数据采集卡原理图

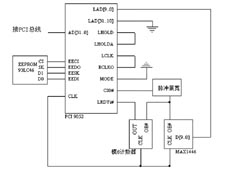

数据采集卡原理图如图2所示。

对原理图有以下几点说明。

(1)设计中采用9052的非复用模式,因此将MODE接地,所以9052的LAD[31..0]上只有数据信息,而其地址信息在LA[27..0]上,又由于MAX1446的转换位数为10bit,因此将该10位输出数据D[9..0]连接到PCI 9052的LAD[9..0],而LAD[31..10]接地。

(2)A/D变换器MAX 1446的时钟频率可高达60MHz。在设计中将PCI总线时钟(33MHz)作为A/D的时钟信号,从而简化了A/D的时钟电路。为了保证LRDYi#信号的产生同MAX 1446的转换同步,模6计数器的时钟信号也采用PCI总线的时钟信号。

(3)数据采集的速率的控制是通过上层的软件完成的。在设计中,将PCI 9052的局部总线端的输出信号CS0#作为A/D的使能信号,驱动A/D的转换功能。CS0#是PCI 9052局部总线端的一个通用片选信号,它是在配置寄存器编程指定的。通过上层软件对CS0#低电平产生的时间间隔的控制,即可实现实现对A/D采样速率的控制。由于A/D转换需要5.5个 时钟周期,在A/D转换期间,使能信号OE#应当始终保持有效,但是CS0#的低电平信号保持时间小于A/D转换时间,因此,使CS0#经过一脉冲展宽电路后再连接到OE#端,以保证A/D的有效转换。

时钟周期,在A/D转换期间,使能信号OE#应当始终保持有效,但是CS0#的低电平信号保持时间小于A/D转换时间,因此,使CS0#经过一脉冲展宽电路后再连接到OE#端,以保证A/D的有效转换。

(4)系统采用的时钟频率为33MHz,由于LRDYi#信号的产生是6个时钟周期,所以数据采集速率可高达55Mbps,可实现对噪声信号的高速实时采样。

结束语

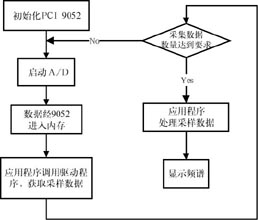

数据采集卡、驱动程序和频谱分析程序三部分的数据流程如图3所示。

1.刘晖译,PCI系统结构(第四版),电子工业出版社,2000.

2.PLX PCI9052 Data Book,2000.

3.Chris Cant著,孙义等译,Windows WDM设备驱动程序开发指南,

机械工业出版社,2000.

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)